# Scheduling and Communication Synthesis for Distributed Real-Time Systems

**Paul Pop**

ISBN 91-7219-776-5 ISSN 0280-7971 PRINTED IN LINKÖPING, SWEDEN BY LINKÖPING UNIVERSITY COPYRIGHT © 2000 PAUL POP

## Lianei

### Abstract

EMBEDDED SYSTEMS ARE now omnipresent: from cellular phones to pagers, from microwave ovens to PDAs, almost all the devices we use are controlled by embedded systems. Many embedded systems have to fulfill strict requirements in terms of performance and cost efficiency. Emerging designs are usually based on heterogeneous architectures that integrate multiple programmable processors and dedicated hardware components. New tools which extend design automation to system level have to support the integrated design of both the hardware and software components of such systems.

This thesis concentrates on aspects of scheduling and communication for embedded real-time systems. Special emphasis has been placed on the impact of the communication infrastructure and protocol on the overall system performance. The scheduling and communication strategies proposed are based on an abstract graph representation which captures, at process level, both the dataflow and the flow of control. We have considered non-preemptive static cyclic scheduling and preemptive scheduling with static priorities for the scheduling of processes, while the communications are statically scheduled according to the time triggered protocol. We have developed static cyclic scheduling algorithms for time-driven systems with control and data dependencies. We show that by considaspects of the communication protocol, improvements can be gained in the schedule quality. In the context of event-driven systems we have proposed a less pessimistic schedulability analysis that is able to handle both control and data dependencies. Moreover, we have provided a schedulability analysis for the time-triggered protocol, and we have proposed several optimization strategies for the synthesis of communication protocol parameters. Extensive experiments as well as real-life examples demonstrate the efficiency of our approaches.

## Acknowledgements

I WOULD LIKE to express thanks towards my advisors Petru Eles and Zebo Peng for their precious guidance during my graduate studies and their valuable comments on the thesis.

Many thanks also to the people at Volvo Technological Development in Gothenburg, especially to Jakob Axelsson, for their insightful ideas during the early stages of this work.

I am also grateful towards my colleagues at IDA and in the ARTES network for providing a creative and pleasant working environment, and towards the administrative and technical staff at IDA, that have always been supportive.

Last, but not least, my deepest gratitude towards my family and friends for their love and encouragement.

## Contents

#### **Introduction 1**

Motivation 2 Problem Formulation 4 Contributions 6 Thesis Overview 7

#### ${\bf System\ Model\ and\ Architecture\ 9}$

Design Representation 9

Conditional Process Graph 10

System Architecture 14

Time vs. Events 14

Hardware Architecture 15

Software Architecture 17

#### Related Work 23

Codesign 24 Scheduling 25 Aspects Related to Communication 29

## Scheduling and Bus Access Optimization for Time Driven Systems 31

Scheduling with Control and Data Dependencies 32

List Scheduling based Algorithm 35

PCP Priority Function 36

Scheduling for Time Driven Systems 38

Scheduling of Messages with the Time Triggered Protocol 40

**Improved Priority Function 42**

Communication Synthesis 45

Experimental Results 49

# Schedulability Analysis and Communication Synthesis for Event Driven Systems 53

Schedulability Analysis 54

Schedulability Analysis with the Time Triggered Protocol 56

Static Single Message Allocation 59

Static Multiple Message Allocation 60

Dynamic Message Allocation 61

**Dynamic Packets Allocation 63**

Schedulability Analysis under Control and Data Dependencies 65

Tasks with Data Dependencies 68

Conditional Process Graphs 71

Communication Synthesis 77

Experimental Results 83

#### **Application 95**

Cruise Controller 96

Experimental Results 97

#### **Conclusions and Future Work 101**

Conclusions 101

Future Work 103

# Chapter 1 Introduction

THIS THESIS CONCENTRATES on aspects related to the scheduling and synthesis of distributed embedded real-time systems consisting of programmable processors and application specific hardware components.

We have investigated the impact of particular communication infrastructures and protocols on the overall performance and how the requirements of such an infrastructure have to be considered for process and communication scheduling. Not only have particularities of the underlying architecture to be considered during scheduling, but the parameters of the communication protocol should also be adapted to fit the particular embedded application.

The approaches to scheduling and system synthesis are based on an abstract graph representation which captures, at process level, both dataflow and the flow of control.

This introductory chapter presents the motivation behind our research, the formulation of the research problems, and our contributions. An overview of the thesis is also presented.

#### 1.1 Motivation

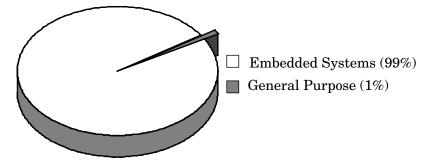

Figure 1.1 presents the microprocessor market share in the year 1999 [Tur99]. As we can see from the figure, less than 1% of the world's microprocessors are used in general purpose systems (i.e., computers). More than 99% are used in embedded real-time systems. Embedded real-time systems are now omnipresent: from cellular phones to pagers, from microwave ovens to PDAs, almost all the devices we use are controlled by embedded systems.

Many embedded systems have to fulfill strict requirements in terms of performance and cost efficiency. Emerging designs are usually based on heterogeneous architectures that integrate multiple programmable processors and dedicated hardware components. New tools which extend design automation to system level have to support the integrated design of both the hardware and software components of such systems.

During the synthesis of an embedded system the designer maps the functionality captured by the input specification on different architectures, trying to find the most cost efficient solution which, at the same time, meets the design requirements [Ern98]. This design process implies the iterative execution of several allocation and partitioning steps before the hardware and software components of the final implementation are generated. The term *hardware/software codesign* is often used to

Figure 1.1: Microprocessor Market Shares

denote this system-level design process. Surveys on this topic can be found in [Mic96, Mic97, Ern98, Gaj95, Sta97, Wol94].

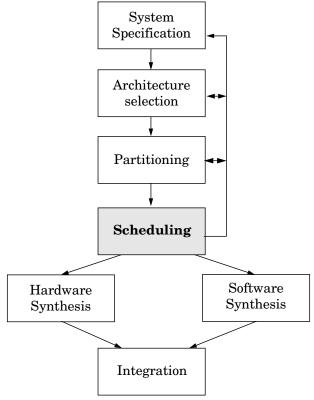

Figure 1.2 presents one possible codesign flow. The design starts with an abstract system specification. The initial system specification is implementation independent which means that no assumptions are made concerning how different parts will later be implemented. Thus, different implementation alternatives can be evaluated, including hardware/software trade-offs.

Moving further into the design process, the designer has to decide what components to include in the hardware architecture and how these components are connected. This is the so called *architecture selection* phase. Following the selection of the archi-

Figure 1.2: A Codesign Flow

tecture components, the designer has to decide what part of the functionality should be implemented on which of the selected components (*mapping*) and what is the execution order of the resulting tasks (*scheduling*).

Scheduling has to be performed during several phases of the design flow. We can, for example, use scheduling for performance estimation during the architecture selection and mapping phases where we are interested to quickly explore design alternatives and compare them in terms of timing behaviour. In addition, scheduling can also be used during the final stages of the design process when we are interested to synthesize the system such that time constraints are fulfilled.

Once a partitioning into hardware and software and a mapping have been decided on, the design process continues with the software synthesis and hardware synthesis phases. In the final phase, the hardware and software parts are integrated and tested. All these design steps can partially overlap, and they can be assisted by (semi)automatic synthesis tools.

In this thesis we concentrate on several aspects related to the scheduling and synthesis of systems consisting of communicating processes which are implemented on multiple processors and dedicated hardware components. In such a system, in which several processes communicate with each other and share resources like processors and buses, scheduling of processes and communications is a factor with a decisive influence on the performance of the system and on the way it meets its timing constraints.

#### 1.2 Problem Formulation

The input for our problem is a model of a real-time system captured using a set of *conditional process graphs* [Ele98a, Ele00] described in detail in Section 2.1.1. Each node in this graph represents one process that can potentially be assigned to one of

#### INTRODUCTION

several programmable or hardware processors. Estimated worst case execution time for each process on each potential host processor is given. We assume that the amount of data to be transferred during communication between two processes has been determined in advance.

We consider a generic architecture consisting of programma-ble processors and application specific hardware processors (ASICs) connected through several buses. As the communication infrastructure for our distributed real-time system we consider the time-triggered protocol (TTP) [Kop94]. TTP is well suited for safety critical distributed real-time embedded systems and represents one of the emerging standards for several application areas like, for example, automotive electronics [Wir98]. Chapter 3 describes in more detail the system architectures considered, with Section 3.2.1 introducing the time-triggered protocol.

In our approach, process scheduling can use either a *non-preemptive static cyclic* or a *static priority preemptive* scheduling approach while the bus communication is statically scheduled according to the TTP. Only one process can be executed at a time by a programmable processor while a hardware processor can execute processes in parallel. Processes on different processors can be executed in parallel. Only one data transfer can be performed by a bus at a given moment. Data transfer on buses and computation can overlap.

Algorithms for automatic hardware/software partitioning have been presented in [Axe96, Ele97, Ern98]. The problems discussed in this thesis concern the performance estimation of a given design alternative and scheduling of processes and communications. Thus, we assume that each process has been assigned to a (programmable or hardware) processor and each communication channel which connects processes assigned to different processors has been assigned to a bus.

In this context, our goals are the following:

• derive a schedulability analysis for systems with both control

and data dependencies,

- derive a schedulability analysis for systems where the communication takes place using the time-triggered protocol,

- determine an as small as possible worst case delay by which the system completes its execution and generate the static schedule such that this delay is guaranteed, and

- determine the parameters of the communication protocol so that the overall system performance is optimized and, thus, the imposed time constraints can be satisfied.

#### 1.3 Contributions

In our approach, an embedded system is viewed as a set of interacting processes mapped on an architecture consisting of several programmable processors and ASICs interconnected by a communication channel.

Process interaction is not only in terms of dataflow but also captures the flow of control, since some processes can be activated depending on conditions computed by previously executed processes.

We have considered both the non-preemptive static cyclic scheduling and the static priority preemptive scheduling approaches for the scheduling of processes, while the communications are statically scheduled according to the TTP.

The scheduling strategies are based on a realistic communication model and execution environment. We take into consideration the overheads due to communications and to the execution environment and consider the requirements of the communication protocol during the scheduling process.

The main contributions of this thesis are:

a less pessimistic schedulability analysis technique in order to bound the response time of a hard real-time system with both control and data dependencies (modelled as a condi-

#### INTRODUCTION

tional process graph) [Pop00b, Pop00c];

- a schedulability analysis in the context of the time-triggered protocol, considering four different approaches to message scheduling [Pop00a, Pop99d];

- a static scheduling strategy for systems with both data and control dependencies, that takes into consideration the overheads due to communications and to the execution environment and considers the requirements of the communication protocol during the scheduling process [Pop99a, Pop99c]; and

- several optimization strategies for the synthesis of the bus access scheme in order to fit the communication particularities of a certain application [Pop00a, Pop99a, Pop99b].

#### 1.4 Thesis Overview

This thesis has 7 chapters, and it is structured as follows:

- Chapter 2 introduces the conditional process graph, describes the hardware and software architectures considered and presents the time-triggered protocol.

- **Chapter 3** presents the related work in the areas of scheduling and communication synthesis, as well as some basic approaches to hardware/software codesign.

- Chapter 4 considers a non-preemptive static scheduling approach both for processes and messages. In such a context, we present previous work on the static cyclic scheduling of systems with data and control dependencies. This work is then extended to handle the scheduling of messages over the TTP. Several approaches to the synthesis of communication parameters for the TTP are proposed and they are later evaluated based on extensive experiments.

- Chapter 5 assumes a preemptive fixed priority scheduling approach for the processes and a non-preemptive static cyclic scheduling approach for the messages, according to the TTP. A schedulability analysis of the TTP is developed considering

#### CHAPTER 1

four message scheduling approaches. This analysis is then extended to systems with data and control dependencies. Optimization strategies that derive the parameters of the communication protocol are proposed. Extensive experiments evaluate the optimization strategies, and show that by considering both data and control dependencies we are able to reduce the pessimism of the analysis.

- **Chapter 6** presents a real-life example. We apply our scheduling and communication synthesis strategies to a vehicle cruise controller, and the results obtained validate our research.

- **Chapter 7** is the final chapter of the thesis and presents our conclusions and future work ideas.

## Chapter 2 System Model and Architecture

THIS CHAPTER PRESENTS preliminaries for the later discussions. We start by introducing the conditional process graph that is used for system modelling, and then continue with the presentation of the hardware architecture considered. Our contribution is the software architecture designed for both time-driven and event-driven systems.

#### 2.1 Design Representation

The specification that is at the input of the design process outlined in Figure 1.2 in the previous chapter could actually be very heterogeneous. Different formalisms are used to specify and model different parts of the system. Then, the information needed for the subsequent design phases, such as architecture selection, partitioning, scheduling, verification, etc., have to be extracted and mapped to internal representations that are more

suited for that purpose. In certain cases, different internal models can be used for different tasks to be performed during system analysis and design.

There is a lot of research in the area of system modelling and specification, and an impressive number of representations have been proposed. An overview and classification of different design representations is given in [Edw97, Ern99].

In this thesis we use the conditional process graph [Ele98, Ele00] as an abstract model for system representation.

#### 2.1.1 CONDITIONAL PROCESS GRAPH

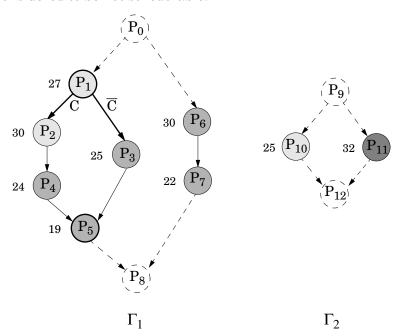

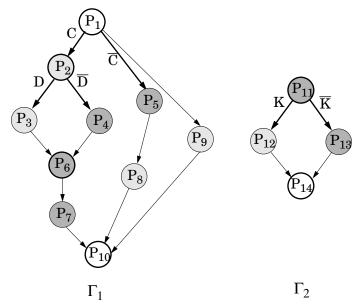

A process graph is an abstract representation consisting of a directed, acyclic, polar graph  $G(V, E_S, E_C)$ . Each node  $P_i \in V$  represents one process.  $E_S$  and  $E_C$  are the sets of simple and conditional edges respectively.  $E_S \cap E_C = \emptyset$  and  $E_S \cup E_C = E$ , where E is the set of all edges. An edge  $e_{ij} \in E$  from  $P_i$  to  $P_j$  indicates that the output of  $P_i$  is the input of  $P_j$ . The graph is polar, which means that there are two nodes, called source and sink, that conventionally represent the first and last process. These nodes are introduced as dummy processes, with zero execution time and no resources assigned, so that all other nodes in the graph are successors of the source and predecessors of the sink respectively.

A mapped process graph,  $\Gamma(V^*, E_S^*, E_C^*, M)$ , is generated from a process graph  $G(V, E_S, E_C)$  by inserting additional processes (communication processes) on certain edges and by mapping each process to a given processing element. The mapping of processes  $P_i \in V^*$  to processors and buses is given by a function  $M: V^* \rightarrow PE$ , where  $PE = \{pe_1, pe_2, ..., pe_{Npe}\}$  is the set of processing elements.  $PE = PP \cup HP \cup B$ , where PP is the set of programmable processors, HP is the set of dedicated hardware components, and B is the set of allocated buses. In certain contexts, we will call both programmable processors and hardware components simply processors. For any process  $P_i$ ,  $M(P_i)$  is the processing ele-

ment to which  $P_i$  is assigned for execution. In the rest of this thesis, when we use the term *conditional process graph* (CPG), we consider a mapped process graph as defined here.

Each process  $P_i$ , assigned to a programmable or hardware processor  $M(P_i)$ , is characterized by an execution time  $t_{P_i}$ .

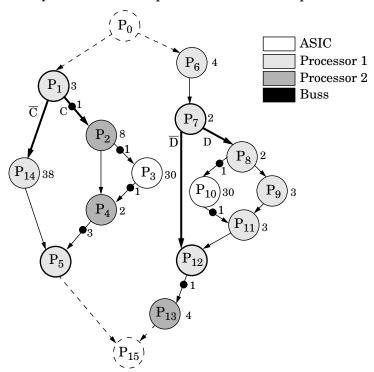

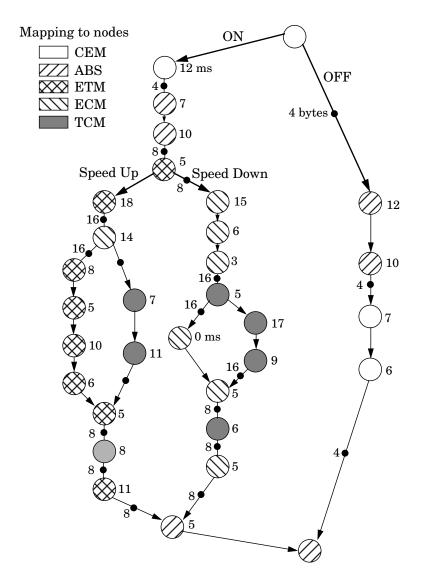

In the process graph depicted in Figure 2.1,  $P_0$  and  $P_{15}$  are the source and sink nodes respectively. The nodes denoted  $P_1, P_2, ..., P_{14}$  are "ordinary" processes specified by the designer. They are assigned to one of the two programmable processors or to the hardware component (ASIC). The rest of the nodes are so called *communication processes* and they are represented in Figure 2.1 as solid circles. They are introduced during the generation of the system representation for each connection which links processes mapped to different processors. These processes model inter-processor com-

Figure 2.1: Conditional Process Graph

munication and their execution time  $t_{i,j}$  (where  $P_i$  is the sender and  $P_j$  the receiver process) is equal to the corresponding communication time. All communications in Figure 2.1 are performed on one bus.

An edge  $e_{ij} \in E_C$  is a conditional edge (represented with thick lines in Figure 2.1) and has an associated condition value. Transmission on such an edge takes place only if the associated condition value is true and not, like on simple edges, for each activation of the input process  $P_i$ . In Figure 2.1 processes  $P_1$  and  $P_7$  have conditional edges at their output.

We call a node with conditional edges at its output a disjunction node (and the corresponding process a disjunction process). A disjunction process has one associated condition, the value of which it computes. Alternative paths starting from a disjunction node, which correspond to complementary values of the condition, are disjoint and they meet in a so called conjunction node (with the corresponding process called conjunction process)<sup>1</sup>. In Figure 2.1 circles representing conjunction and disjunction nodes are depicted with thick borders. The alternative paths starting from disjunction node  $P_1$ , which computes condition C, meet in conjunction node  $P_5$ . We assume that conditions are independent and alternatives starting from different processes cannot depend on the same condition.

A process, that is not a conjunction process, can be activated only after all its inputs have arrived. A conjunction process can be activated after messages coming on one of the alternative paths have arrived. All processes issue their outputs when they terminate. If we consider the activation time of the source process as a reference, the activation time of the sink process is the delay of the system at a certain execution. This delay has to be, in the worst case, smaller than a certain imposed deadline. Release

<sup>1.</sup> If no process is specified on an alternative path, it is modelled by a conditional edge from the disjunction to the corresponding conjunction node (a communication process may be inserted on this edge at mapping).

times of some processes as well as multiple deadlines can be easily modelled by inserting dummy nodes between certain processes and the source or the sink node respectively. These dummy nodes represent processes with a certain execution time but which are not allocated to any processing element.

A boolean expression  $X_{Pi}$ , called a guard, can be associated to each node  $P_i$  in the graph. It represents the necessary conditions for the respective process to be activated.  $X_{Pi}$  is not only necessary but also sufficient for process  $P_i$  to be activated during a given system execution. Thus, two nodes  $P_i$  and  $P_j$ , where  $P_j$  is not a conjunction node, are connected by an edge  $e_{ij}$  only if  $X_{Pj} \Rightarrow X_{Pi}$  (which means that  $X_{Pi}$  is true whenever  $X_{Pj}$  is true). This avoids specifications in which a process is blocked even if its guard is true, because it waits for a message from a process which will not be activated. If  $P_j$  is a conjunction node, predecessor nodes  $P_i$  can be situated on alternative paths corresponding to a condition.

The above execution semantics is that of a so called single rate system. It assumes that a node is executed at most once for each activation of the system. If processes with different periods have to be handled, this can be solved by generating several instances of the processes and building a CPG which corresponds to a set of processes as they occur within a time period that is equal to the least common multiple of the periods of the involved processes.

As mentioned, we consider execution times of processes, as well as the communication times, to be given. In the Figure 2.1 they are depicted to the right of each node. In the case of hard real-time systems this will, typically, be worst case execution times and their estimation has been extensively discussed in the literature [Eng99, Li95, Lun99, Mal97]. For many applications, actual execution times of processes are depending on the current data and/or the internal state of the system. By explicitly capturing the control flow in our model, we allow for a more fine-tuned modeling and a tighter (less pessimistic) assignment of

worst case execution times to processes, compared to traditional data-flow based approaches.

#### 2.2 System Architecture

As pointed out in the introductory chapter, real-time systems are nowadays omnipresent. Depending on the particular application implemented, real-time systems can be implemented as uniprocessor, multiprocessor, or distributed. Systems can be hard or soft, event-driven or time-driven, fault-tolerant, autonomous, etc. A good classification of real-time systems is given in [Kop97a].

This chapter describes the architecture we consider in this thesis for the implementation of a distributed real-time system. Our hardware architecture consists of a set of nodes interconnected by a communication channel that uses the time-triggered protocol as the communication protocol. The software architecture depends on the triggering mechanisms for the start of communication and processing activities.

#### 2.2.1 TIME VS. EVENTS

According to [Kop97a] a *trigger* is "an event that causes the start of some action, e.g., the execution of a task or the transmission of a message." Different approaches to the design of real-time systems can be identified, based on the triggering mechanisms for the processing and communication: *event-triggered* or *time-triggered*.

In the event-triggered approach all the activities happen when a significant change of state occurs. The significant events are brought to the attention of the CPU by the interrupt mechanism. Event-triggered systems typically require preemptive priority-based scheduling, where the appropriate process is invoked to service the event.

In the time-triggered approach all the activities are initiated at predetermined points in time. Thus, there is only one interrupt in each node of a distributed time-triggered system, the time interrupt. In a distributed time-triggered system it is assumed that the clocks of all nodes are synchronized to provide a global notion of time. Time-triggered systems typically require non-preemptive static cyclic scheduling, where the process activation or message communication is done based on a schedule table built off-line.

We consider the time-triggered protocol for the communication infrastructure, and thus, the communication of messages is time-triggered. However, depending on the particular application, the activation of processes can be either time-triggered (Chapter 4) or event-triggered (Chapter 5).

#### 2.2.2 HARDWARE ARCHITECTURE

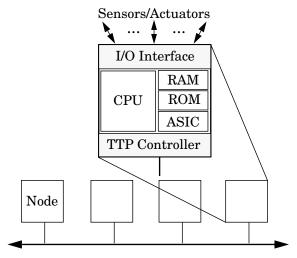

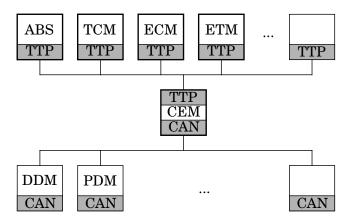

We consider architectures consisting of nodes connected by a broadcast communication channel (Figure 2.2). Every node consists of a TTP controller [Kop97b], a CPU, a RAM, a ROM and an I/O interface to sensors and actuators. A node can also have an ASIC in order to accelerate parts of its functionality.

Time Triggered Protocol. Communication between nodes is based on the time-triggered protocol (TTP) [Kop94]. TTP was designed for distributed real-time applications that require predictability and reliability (e.g, drive-by-wire). It integrates all the services necessary for fault-tolerant real-time systems. TTP services of importance to our problems are: message transport with acknowledgment and predictable low latency, clock synchronization within the microsecond range and rapid mode changes.

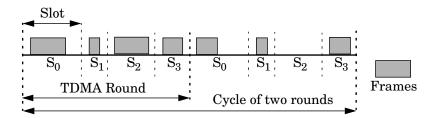

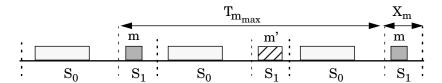

The communication channel is a broadcast channel, so a message sent by a node is received by all the other nodes. The bus access scheme is time-division multiple-access (TDMA) (Figure

**Figure 2.2:** System Architecture

2.3). Each node  $N_i$  can transmit only during a predetermined time interval, the so called TDMA slot  $S_i$ . In such a slot, a node can send several messages packaged in a frame. We consider that a slot  $S_i$  is at least large enough to accommodate the largest message generated by any process assigned to node  $N_i$ , so the messages do not have to be split in order to be sent. A sequence of slots corresponding to all the nodes in the architecture is called a TDMA round. A node can have only one slot in a TDMA round. Several TDMA rounds can be combined together in a cycle that is repeated periodically. The sequence and length of the slots are the same for all the TDMA rounds. However, the length and contents of the frames may differ.

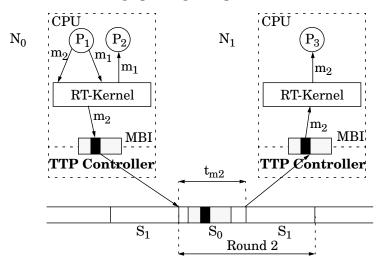

Every node has a TTP controller that implements the protocol services, and runs independently of the node's CPU. Communication with the CPU is performed through a so called message base interface (MBI) which is usually implemented as a dual ported RAM (Figure 2.4).

The TDMA access scheme is imposed by a so called message descriptor list (MEDL) that is located in every TTP controller.

Figure 2.3: Buss Access Scheme

The MEDL basically contains: the time when a frame has to be sent or received, the address of the frame in the MBI and the length of the frame. MEDL serves as a schedule table for the TTP controller which has to know when to send or receive a frame to or from the communication channel.

The TTP controller provides each CPU with a timer interrupt based on a local clock, synchronized with the local clocks of the other nodes. The clock synchronization is done by comparing the a-priori known time of arrival of a frame with the observed arrival time. By applying a clock synchronization algorithm, TTP provides a global time-base of known precision, without any overhead on the communication.

Information transmitted on the bus has to be properly formatted in a frame. A TTP frame has the following fields: start of frame, control field, data field, and CRC field. The data field can contain one or more application messages.

#### 2.2.3 Software Architecture

We have designed two distinct software architectures: one for time-triggered systems, and another for event-triggered systems. The main component of both software architectures is a real-time kernel that runs on top of each node of the architecture. **Time Triggered Systems.** Each kernel in the software architecture for the time-triggered systems has a schedule table. This schedule table contains all the information needed to take decisions on activation of processes and transmission of messages, based on the values of conditions (Table 4.1).

In order to run a predictable hard real-time application the overhead of the kernel and the worst case administrative overhead (WCAO) of every system call has to be determined. Having a time-triggered system, all the activity is derived from the progression of time which means that there are no other interrupts except for the timer interrupt.

Several activities, like polling of the I/O or diagnostics, take place directly in the timer interrupt routine. The overhead due to this routine is expressed as the utilization factor  $U_t$ .  $U_t$  represents a fraction of the CPU power utilized by the timer interrupt routine, and has an influence on the execution times of the processes.

We also have to take into account the overheads for process activation and message passing. For process activation we con-

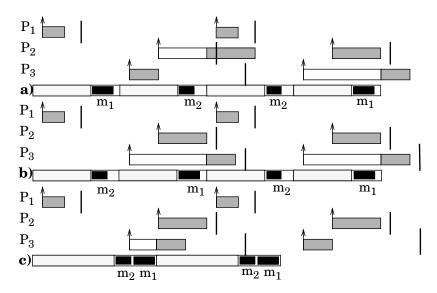

Figure 2.4: Message Passing, Time-Driven Systems

sider an overhead  $\delta_{PA}$ . The message passing mechanism is illustrated in Figure 2.4, where we have three processes,  $P_1$  to  $P_3$ .  $P_1$  and  $P_2$  are mapped to node  $N_0$  that transmits in slot  $S_0$ , and  $P_3$  is mapped to node  $N_1$  that transmits in slot  $S_1$ . Message  $m_1$  is transmitted between  $P_1$  and  $P_2$  that are on the same node, while message  $m_2$  is transmitted from  $P_1$  to  $P_3$  between the two nodes. We consider that each process has its own memory locations for the messages it sends or receives and that the addresses of the memory locations are known to the kernel through the schedule table.

$P_1$  is activated according to the schedule table, and when it finishes it calls the send kernel function in order to send  $m_1$ , and then  $m_2$ . Based on the schedule table, the kernel copies  $m_1$  from the corresponding memory location in  $P_1$  to the memory location in  $P_2$ . The time needed for this operation represents the WCAO  $\delta_S$  for sending a message between processes located on the same node<sup>1</sup>. When  $P_2$  will be activated it finds the message in the right location. According to our scheduling policy, whenever a receiving process needs a message, the message is already placed in the corresponding memory location. Thus, there is no overhead on the receiving side, for messages exchanged on the same node.

Message  $m_2$  has to be sent from node  $N_0$  to node  $N_1$ . At a certain time, known from the schedule table, the kernel transfers  $m_2$  to the TTP controller by packaging  $m_2$  into a frame in the MBI. The WCAO of this function is  $\delta_{KS}$ . Later on, the TTP controller knows from its MEDL when it has to take the frame from the MBI, in order to broadcast it on the bus. In our example the timing information in the schedule table of the kernel and the MEDL is determined in such a way that the broadcasting of the frame is done in the slot  $S_0$  of  $Round\ 2$ . The TTP controller of

<sup>1.</sup> Overheads  $\delta_S$ ,  $\delta_{KS}$  and  $\delta_{KR}$  depend on the length of the transferred message; in order to simplify the presentation this aspect is not discussed further.

node  $N_1$  knows from its MEDL that it has to read a frame from slot  $S_0$  of  $Round\ 2$  and to transfer it into the MBI. The kernel in node  $N_1$  will read the message  $m_2$  from the MBI, with a corresponding WCAO of  $\delta_{KR}$ . When  $P_3$  will be activated based on the local schedule table of node  $N_1$ , it will already have  $m_2$  in its right memory location.

**Event Triggered Systems.** Each kernel in the software architecture for the event-triggered systems has a so called tick scheduler. The tick scheduler is activated periodically by the timer interrupts and decides on activation of processes, based on their priorities. Several activities, like polling of the I/O or diagnostics, take also place in the timer interrupt routine.

As in the previous section, the overhead of the kernel and the worst case administrative overhead (WCAO) of every system call have to be determined. Our schedulability analysis takes into account these overheads, and also the overheads due to the message passing.

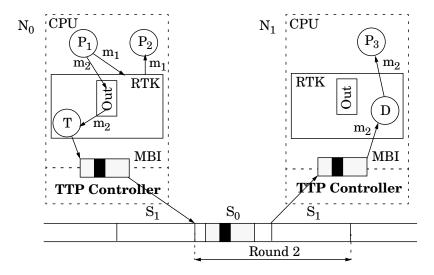

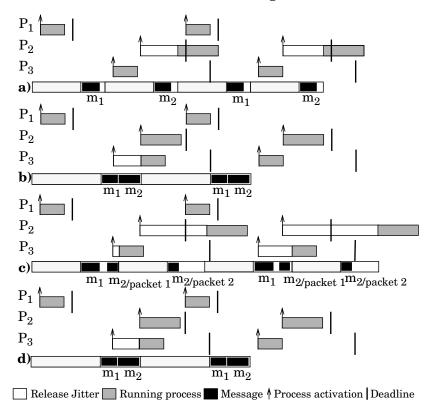

Figure 2.5: Message Passing, Event-Driven Systems

The message passing mechanism is illustrated in Figure 2.5, where we have three processes,  $P_1$  to  $P_3$ .  $P_1$  and  $P_2$  are mapped to node  $N_0$  that transmits in slot  $S_0$ , and  $P_3$  is mapped to node  $N_1$  that transmits in slot  $S_1$ . Message  $m_1$  is transmitted between  $P_1$  and  $P_2$  that are on the same node, while message  $m_2$  is transmitted from  $P_1$  to  $P_3$  between the two nodes.

Messages between processes located on the same processor are passed through shared protected objects. The overhead for their communication is accounted for by the blocking factor, computed according to the priority ceiling protocol [Sha90].

Message  $m_2$  has to be sent from node  $N_0$  to node  $N_1$ . Thus, after  $m_2$  is produced by  $P_1$ , it will be placed into an outgoing message queue, called Out. The access to the queue is guarded by a priority-ceiling semaphore. A so called transfer process (denoted with T in Figure 2.5) moves the message from the Out queue into the MBI.

How the message queue is organized and how the message transfer process selects the particular messages and assembles them into a frame, depends on the particular approach chosen for message scheduling (see Section 5.1). The message transfer process is activated at certain a priori known moments, by the tick scheduler in order to perform the message transfer. These activation times are stored in a message handling time table (MHTT) available to the real-time kernel in each node. Both the MEDL and the MHTT are generated off-line as result of the schedulability analysis and optimization which will be discussed later. The MEDL imposes the times when the TTP controller of a certain node has to move frames from the MBI to the communication channel. The MHTT contains the times when messages have to be transferred by the message transfer process from the Out queue into the MBI, in order to further be broadcasted by the TTP controller. As result of this synchronization, the activation times in the MHTT are directly related to those in the MEDL and the first table results directly from the second one.

It is easy to observe that we have the most favourable situation when, at a certain activation, the message transfer process finds in the *Out* queue all the "expected" messages which then can be packed into the just following frame to be sent by the TTP controller. However, application processes are not statically scheduled and availability of messages in the *Out* queue can not be guaranteed at fixed times. Worst case situations have to be considered, as will be shown in Section 5.1.

Let us come back to Figure 2.5. There we assumed a context in which the broadcasting of the frame containing message  $m_2$  is done in the slot  $S_0$  of Round 2. The TTP controller of node  $N_1$ knows from its MEDL that it has to read a frame from slot  $S_0$  of Round 2 and to transfer it into its MBI. In order to synchronize with the TTP controller and to read the frame from the MBI, the tick scheduler on node  $N_1$  will activate, based on its local MHTT, a so called delivery process, denoted with D in Figure 2.5. The delivery process takes the frame from the MBI, and extracts the messages from it. For the case when a message is split into several packets, sent over several TDMA rounds, we consider that a message has arrived at the destination node after all its corresponding packets have arrived. When  $m_2$  has arrived, the delivery process copies it to process  $P_3$  which will be activated. Activation times for the delivery process are fixed in the MHTT just as explained earlier for the message transfer process.

The number of activations of the message transfer and delivery processes depends on the number of frames transferred, and they are taken into account in our analysis, as well as the delay implied by the propagation on the communication bus.

## Chapter 3 Related Work

A LOT HAS BEEN published in the last years in the areas of hardware/software codesign and real-time systems research. The intent of this chapter is to give a brief overview of the previous research on codesign with an emphasis on scheduling and communication synthesis.

The aspects of our work that differ from the related research presented in this chapter are:

- we consider a more complex system model that is able to capture both the flow of data and that of control;

- our system architectures are heterogeneous and consider a realistic communication model based on the time-triggered protocol;

- we consider issues related to the interaction between scheduling of processes and communication scheduling; and

- we have provided system level communication synthesis strategies that lead to significant improvements on the performance of the system.

#### 3.1 Hardware/Software Codesign

Section 1.1 has introduced hardware/software codesign (shorter, codesign) and presented a possible codesign flow. The intention of this section is to provide a short overview of this emerging research area. For more details, the reader is referred to several surveys on this topic [Mic96, Mic97, Ern98, Gaj95, Sta97, Wol94].

Codesign is a relatively new research area. The "First International Workshop on Hardware/Software Codesign" has taken place in 1992, and has been an yearly event since then. Around the same time hardware/software codesign tracks and sessions have started to appear at important Electronic Design Automation (EDA) conferences like DAC, DATE, ICCAD, ISSS, etc.

The initial assumptions of codesign were quite restrictive, and the goals modest. For example, several researchers have assumed a simple specification in form of a computer program, and the main goal was to obtain an as high as possible execution performance within a given cost (acceleration). The architecture considered consisted of a single processor together with an ASIC used to accelerate parts of the functionality [Cho95a, Gup95, Moo97]. In this context, the main problems were to divide the functionality between the ASIC and the CPU (hardware/software partitioning) [Ele97, Ern93, Gup93, Vah94], to automatically generate drivers and other components related to communication (communication synthesis) [Cho92, Wal94] and to simulate and verify the resulting system (cosimulation and coverification) [Val95, Val96]. However, today the initial assumptions are no longer valid and the goals are much broader [Bol97, Dav98, Dav99, Dic98, Lak99, Ver96]:

The applications are heterogeneous, consisting of hardware and software components. Both hardware and software can be data or control dominated, and hardware can be both digital and analog.

- The specification for such applications is inherently heterogeneous and complex. Several languages as well as several models of computation can be found within a specification.

- The architectures are varied ranging from distributed embedded systems, in the automotive electronics area, to systems on a chip used in telecommunications.

- The goals include not only acceleration with minimal hardware cost, but also issues related to the reuse of legacy hardware and software subsystems, real-time constraints, quality of service, fault tolerance and dependability, power consumption, flexibility, time-to-market, etc.

#### 3.2 Scheduling

Process scheduling for performance estimation and synthesis of real-time systems has been intensively researched in the last years. The existing approaches differ in the scheduling strategy adopted, system architectures considered, handling of the communication and process interaction aspects. However, our main distinction in this section will be made between non-preemptive static cyclic scheduling and preemptive fixed-priority scheduling. We have to mention that performance estimation and scheduling of processes typically requires, as an input, estimated execution times of single processes [Eng99, Ern97, Gon95, Hen95, Li95, Lun99, Mal97, Suz96].

**Non-preemptive static cyclic scheduling.** Static cyclic scheduling of a set of data dependent software processes on a multiprocessor architecture has been intensively researched [Kop97a, Xu00].

Several approaches are based on list scheduling heuristics using different priority criteria [Cof72, Deo98, Jor97, Kwo96, Wu90] or on branch-and-bound algorithms [Kas84]. These approaches are based on the assumption that a number of iden-

tical processors are available to which processes are progressively assigned as the static schedule is elaborated. Such an assumption is obviously not acceptable for distributed embedded systems which are heterogeneous by nature. In [Jor97] a list scheduling based approach is extended to handle heterogeneous architectures. Scheduling is performed by progressively assigning tasks to the allocated processors with the goal to minimize the length of the schedule. The proposed algorithm handles only processors which execute one single process at a time (not typical for hardware) and the resulting partitioning does not take into consideration any design constraints.

In [Ben96, Pra92] static scheduling and partitioning of processes, and allocation of system components, are formulated as a mixed integer linear programming (MILP) problem. A disadvantage of this approach is the complexity of solving the MILP model. The size of such a model grows quickly with the number of processes and allocated resources. In [Kuc97] a formulation using constraint logic programming has been proposed for similar problems.

In all the previous approaches process interaction is only in terms of dataflow. However, when including control dependencies significant improvements in the quality of the resulting schedules can be obtained [Ele98a]. Section 4.1 presents in more detail related research on the static scheduling for systems with control and data dependencies that is used as a starting point for our work.

It has been claimed [Xu93] that static cyclic scheduling approach is the only approach that can solve a certain class of problems. However, advances in the area of fixed priority preemptive scheduling show that such classes of problems can also be handled with other scheduling strategies [Aud93, Tin94b].

**Fixed priority preemptive scheduling.** Preemptive scheduling of independent processes with static priorities running on single processor architectures has its roots in [Liu73]. The approach has been later extended to accommodate more general computational models and has also been applied to distributed systems [Tin94a]. The reader is referred to [Aud95, Bal98, Sta93] for surveys on this topic.

In [Yen97] performance estimation is based on a preemptive scheduling strategy with static priorities using rate monotonic analysis. In [Lee99] an earlier deadline first strategy is used for non-preemptive scheduling of processes with possible data dependencies. Preemptive and non-preemptive static scheduling are combined in the cosynthesis environment described in [Dav98, Dav99].

In many of the previous scheduling approaches researchers have assumed that processes are scheduled independently. However, this is not the case in reality, where process sets can exhibit both data and control dependencies. Moreover, knowledge about these dependencies can be used in order to improve the accuracy of schedulability analyses and the quality of produced schedules.

One way of dealing with data dependencies between processes with static priority based scheduling has been indirectly addressed by the extensions proposed for the schedulability analysis of distributed systems through the use of the *release jitter* [Tin94b]. Release jitter is the worst case delay between the arrival of a process and its release (when it is placed in the runqueue for the processor) and can include the communication delay due to the transmission of a message on the communication channel.

Tindell et al. [Tin94b] and Yen et al. [Yen98] use time offset relationships and phases, respectively, in order to model data dependencies. Offset and phase are similar concepts that express the existence of a fixed interval in time between the arrivals of sets of processes. The authors show that by introducing such concepts into the computational model, the pessimism of the analysis is significantly reduced when bounding the time behaviour of the system. The work has been later extended with the concept of dynamic offsets [Pal98]. The works by [Tin94b] and [Yen98] are further detailed in Section 5.2 that introduces the schedulability analysis for the time-triggered protocol. Also, a brief introduction to schedulability analysis is presented in Section 5.1.

When control dependencies exist then, depending on conditions, only a subset of the set of processes is executed during an invocation of the system. Modes have been used to model a certain class of control dependencies [Foh93]. Such a model basically assumes that at the starting of an execution cycle, a particular functionality is known in advance and is fixed for one or several cycles until another mode change is performed. However, modes cannot handle fine grained control dependencies, or certain combinations of data and control dependencies. Careful modeling using the *periods* of processes (lower bound between subsequent re-arrivals of a process) can also be a solution for some cases of control dependencies [Ger96]. If, for example, we know that a certain set of processes will only execute every second cycle of the system, we can set their periods to the double of the period of the rest of the processes in the system. However, using the worst case assumption on periods leads very often to unnecessarily pessimistic schedulability evaluations. More refined process models can produce much better schedulability results, as will be later shown in the thesis. Recent works [Bar98a, Bar98b] aim at extending the existing models to handle control dependencies. In [Bar98b] Baruah introduces the recurring real-time task model that is able to capture lower level control dependencies, and presents an exponential-time analysis for uniprocessor systems.

## 3.3 Aspects Related to Communication

Currently, more and more real-time systems are used in physically distributed environments and have to be implemented on distributed architectures in order to meet reliability, functional, and performance constraints. However, researchers have often ignored or very much simplified aspects concerning the communication infrastructure.

One typical approach is to consider communication processes as processes with a given execution time (depending on the amount of information exchanged) and to schedule them as any other process, without considering issues like communication protocol, bus arbitration, packaging of messages, clock synchronization, etc. These aspects are, however, essential in the context of safety-critical distributed real-time applications and one of our objectives is to develop a strategy which takes them into consideration for process scheduling.

Many efforts dedicated to communication synthesis have concentrated on the synthesis support for the communication infrastructure but without considering hard real-time constraints and system level scheduling aspects [Cho95b, Dav95, Knu99, Nar94]. Lower level communication synthesis aspects under timing constraints have been addressed in [Ort98, Knu99].

We have to mention here some results obtained in extending real-time schedulability analysis so that network communication aspects can be handled. In [Tin95], for example, the CAN protocol is investigated while the work reported in [Erm97] considers systems based on the ATM protocol. Analysis for a simple TDMA protocol is provided in [Tin94a] that integrates processor and communication schedulability and provide a "holistic" schedulability analysis in the context of distributed real-time systems.

### CHAPTER 3

# Chapter 4 Scheduling and Bus Access Optimization for Time Driven Systems

IN THIS CHAPTER we consider time-driven distributed realtime systems that use the time-triggered protocol for the communication infrastructure. Thus, both the activation of processes and the transmission of messages are done based on the progression of time.

The chapter starts by presenting an approach to static scheduling under control and data dependencies for distributed real-time systems [Dob98, Ele98a, Ele00]. The approach considers a simplified communication model in which the execution time of the communication processes depends only on the amount of data exchanged by the processes engaged in the communication. The communication processes are treated exactly as ordinary processes during scheduling, and the bus is modelled similar to a programmable processor that can "execute" one communication at a time as soon as the communication becomes "ready".

We propose in this chapter several extensions to this approach:

- scheduling of messages using a realistic communication model based on the time-triggered protocol (Section 4.2.1);

- a new priority function for list scheduling that uses knowledge about the bus access scheme in order to improve the schedule quality (Section 4.2.2); and

- optimization strategies for the synthesis of parameters of the communication protocol, aimed at improving the schedule quality (Section 4.2.3).

# 4.1 Scheduling with Control and Data Dependencies

In our approach, we consider distributed hard-real time systems modelled using conditional process graphs.

Optimal scheduling has been proven to be an NP complete problem [Ull75] in even simpler contexts than those characteristic to distributed systems represented as CPGs. Thus, it is essential to develop heuristics which produce good quality results in a reasonable time.

In [Dob98, Ele98a, Ele00] the authors concentrate on developing a scheduling algorithm for systems with both control and data dependencies, modelled using the conditional process graph. According to this model, some processes can only be activated if certain conditions, computed by previously executed processes, are fulfilled. Thus, process scheduling is complicated since at a given activation of the system, only a certain subset of the total amount of processes is executed and this subset differs from one activation to the other.

The output produced by their scheduling algorithm is a schedule table that contains all the information needed by a distributed run time scheduler to take decisions on activation of processes. It is considered that during execution a very simple

#### TIME DRIVEN SYSTEMS

non-preemptive scheduler located in each processing element decides on process and communication activation depending on the actual values of conditions. Only one part of the table has to be stored in each processor, namely the part concerning decisions which are taken by the corresponding scheduler.

Under these assumptions, Table 4.1 presents a possible schedule (produced by the algorithm in Figure 4.1) for the conditional process graph in Figure 2.1. In Table 4.1 there is one row for each "ordinary" or communication process, which contains activation times corresponding to different values of conditions. Each column in the table is headed by a logical expression constructed as a conjunction of condition values. Activation times in a given column represent starting times of the processes when the respective expression is true.

According to the schedule in Table 4.1 process  $P_I$  is activated unconditionally at the time 0, given in the first column of the table. However, activation of some processes at a certain execution depends on the values of the conditions, which are unpredictable. For example, process  $P_{II}$  has to be activated at t=44 if  $C \land D$  is true and t=52 if  $\overline{C} \land D$  is true. At a certain moment during the execution, when the values of some conditions are already known, they have to be used in order to take the best possible decisions on when and which process to activate. Therefore, after the termination of a process that produces a condition (disjunction process), the value of the condition is broadcasted from the corresponding processor to all other processors. This broadcast is scheduled as soon as possible on the communication channel, and is considered together with the scheduling of the messages.

To produce a deterministic behaviour, which is correct for any combination of conditions, the table has to fulfill several requirements:

1. No process will be activated if, for a given execution, the con-

- ditions required for its activation are not fulfilled.

- 2. Activation times have to be uniquely determined by the conditions.

- 3. Activation of a process  $P_i$  at a certain time t has to depend

**Table 4.1:** Schedule Table for Graph in Figure 2.1

| process            | true | C | C∧D | $\mathbf{C} \wedge \overline{\mathbf{D}}$ | $\overline{\mathbf{C}}$ | $\overline{\mathbf{C}} \wedge \mathbf{D}$ | $\overline{\mathbf{C}} \wedge \overline{\mathbf{D}}$ |

|--------------------|------|---|-----|-------------------------------------------|-------------------------|-------------------------------------------|------------------------------------------------------|

| P <sub>1</sub>     | 0    |   |     |                                           |                         |                                           |                                                      |

| $P_2$              |      | 5 |     |                                           |                         |                                           |                                                      |

| $P_3$              |      |   | 14  | 14                                        |                         |                                           |                                                      |

| P <sub>4</sub>     |      |   | 45  | 45                                        |                         |                                           |                                                      |

| $P_5$              |      |   | 51  | 50                                        |                         | 55                                        | 47                                                   |

| P <sub>6</sub>     |      | 3 |     |                                           | 3                       |                                           |                                                      |

| $P_7$              |      | 7 |     |                                           | 7                       |                                           |                                                      |

| P <sub>8</sub>     |      |   | 9   |                                           |                         | 9                                         |                                                      |

| P <sub>9</sub>     |      |   | 11  |                                           |                         | 11                                        |                                                      |

| P <sub>10</sub>    |      |   | 13  |                                           |                         | 13                                        |                                                      |

| P <sub>11</sub>    |      |   | 44  |                                           |                         | 52                                        |                                                      |

| P <sub>12</sub>    |      |   | 47  | 9                                         |                         | 55                                        | 9                                                    |

| P <sub>13</sub>    |      |   | 48  | 13                                        |                         | 56                                        | 11                                                   |

| P <sub>14</sub>    |      |   |     |                                           |                         | 14                                        | 9                                                    |

| P <sub>1,2</sub>   |      | 4 |     |                                           |                         |                                           |                                                      |

| P <sub>4,5</sub>   |      |   | 48  | 47                                        |                         |                                           |                                                      |

| P <sub>2,3</sub>   |      |   | 13  | 13                                        |                         |                                           |                                                      |

| P <sub>3,4</sub>   |      |   | 44  | 44                                        |                         |                                           |                                                      |

| P <sub>12,13</sub> |      |   | 47  | 10                                        |                         | 55                                        |                                                      |

| P <sub>8,10</sub>  |      |   | 12  |                                           |                         | 12                                        |                                                      |

| P <sub>10,11</sub> |      |   | 43  |                                           |                         | 43                                        |                                                      |

| С                  |      | 3 |     |                                           |                         | 11                                        | 9                                                    |

| D                  |      |   | 11  | 9                                         |                         | 11                                        | 9                                                    |

#### TIME DRIVEN SYSTEMS

only on condition values which are determined at the respective moment t and are known to the processing element which executes  $P_i$ .

#### 4.1.1 LIST SCHEDULING BASED ALGORITHM

As the starting point for our improved scheduling technique that is tailored for time-triggered embedded systems we consider the list scheduling based algorithm in [Dob98, Ele00] presented, in a very simplified form, in Figure 4.1.

```

ListScheduling(CurrentTime, ReadyList, KnownConditions)

repeat

Update(ReadyList)

for each processing element PE

if PE is free at CurrentTime then

P_i = \text{GetReadyProcess}(ReadyList)

if there exists a P_i then

Insert(P<sub>i</sub>, ScheduleTable, CurrentTime, KnownConds)

if P_i is a disjunction process then

C_i = condition calculated by P_i

ListScheduling(CurrentTime,

ReadyList ∪ ready nodes from the true branch,

KnownConditions ∪ true C<sub>i</sub>)

ListScheduling(CurrentTime,

ReadyList ∪ ready nodes from the false branch,

KnownConditions \cup false C_i

end if

end if

end if

end for

CurrentTime = time when a scheduled process terminates

until all processes of this alternative path are scheduled

end ListScheduling

```

Figure 4.1: List Scheduling Based Algorithm

List scheduling heuristics [Ele98b] are based on priority lists from which processes are extracted in order to be scheduled at certain moments. In the algorithm presented in Figure 4.1, there is such a list, ReadyList, that contains the processes which are eligible to be activated on the corresponding processor at time CurrentTime. These are processes which have not been yet scheduled but have all predecessors already scheduled and terminated.

The ListScheduling function is recursive and calls itself for each disjunction node in order to separately schedule the nodes in the true branch, and those in the false branch respectively. Thus, the alternative paths are not activated simultaneously and resource sharing is correctly achieved (for details on how the algorithm fulfils the three requirements on the schedule table we refer to [Ele00]).

An essential component of a list scheduling heuristic is the priority function used to solve conflicts between ready processes. The highest priority process will be extracted by function GetReadyProcess from the ReadyList in order to be scheduled.

#### 4.1.2 PCP Priority Function

Priorities for list scheduling very often are based on the critical path (CP) from the respective process to the sink node. Thus, for CP scheduling, the priority assigned to a process  $P_i$  will be the maximal execution time from the current node to the sink:

$$l_{Pi} = \max_{k} \sum_{P_j \in \pi_{ik}} t_{Pj} \,,$$

where  $\pi_{ik}$  is the kth path from node.

Considering the concrete definition of the problem, significant improvements of the resulting schedule can be obtained, without any penalty in scheduling time, by making use of the available information on process allocation [Ele98b].

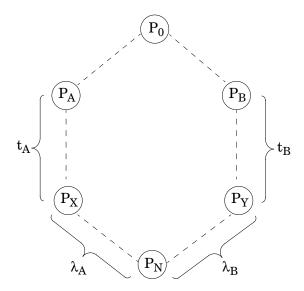

Let us consider the graph in Figure 4.2 and suppose that the list scheduling algorithm has to decide between scheduling proc-

Figure 4.2: Delay estimation for PCP scheduling

ess  $P_A$  or  $P_B$  which are both ready to be scheduled on the same programmable processor or bus  $pe_i$ . In Figure 4.2 we depicted only the critical path from  $P_A$  and  $P_B$  to the sink node. Let us consider that  $P_X$  is the last successor of  $P_A$  on the critical path such that all processes from  $P_A$  to  $P_X$  are assigned to the same processing element  $pe_i$ . The same holds for  $P_Y$  relative to  $P_B$ .  $t_A$  and  $t_B$  are the total execution time of the chain of processes from  $P_A$  to  $P_X$  and from  $P_B$  to  $P_Y$  respectively, following the critical paths.  $\lambda_A$  and  $\lambda_B$  are the total execution times of the processes on the rest of the two critical paths. Thus, we have:

$l_{PA} = t_A + \lambda_A$ , and  $l_{PB} = t_B + \lambda_B$ .

However, [Ele98b] does not use the length of these critical paths as a priority. The policy in [Ele98b] is based on the estimation of a lower bound L on the total delay, taking into consideration that the two chains of processes  $P_A$ - $P_X$  and  $P_B$ - $P_Y$  are executed on the same processor.  $L_{PA}$  and  $L_{PB}$  are the lower bounds if  $P_A$  and  $P_B$  respectively are scheduled first:

$$\begin{split} L_{PA} &= \max(T\_current + t_A + \lambda_A, T\_current + t_A + t_B + \lambda_B) \\ L_{PB} &= \max(T\_current + t_B + \lambda_B, T\_current + t_B + t_A + \lambda_A) \end{split}$$

The alternative that offers the perspective of the shorter delay  $L = \min(L_{PA}, L_{PB})$  is selected. It can be observed that if  $\lambda_A > \lambda_B$  then  $L_{PA} < L_{PB}$ , which means that we have to schedule  $P_A$  first so that  $L = L_{PA}$ ; similarly if  $\lambda_B > \lambda_A$  then  $L_{PB} < L_{PA}$ , and we have to schedule  $P_B$  first in order to get  $L = L_{PB}$ .

# 4.2 Scheduling for Time Driven Systems

We propose several extensions to the scheduling algorithm briefly described in Section 4.1. The extensions consider a realistic communication and execution infrastructure, and include aspects of the communication protocol in the optimization process.

Thus, as an input to our problem we consider a safety-critical application that has several operating modes, and each mode is modelled by a conditional process graph. The architecture of the system is given as described in the Section 2.2. Each process of the process graph is mapped on a CPU or an ASIC of a node. The worst case execution time (WCET) for each process mapped on a processing element is known, as well as the length  $b_{mi}$  of each message.

We are interested to derive a worst case delay on the system execution time for each operating mode, so that this delay is as small as possible, and to synthesize the local schedule tables for each node, as well as the MEDL for the TTP controllers, which guarantee this delay.

Considering the concrete definition of our problem, the communication time is no longer dependent only on the length of the message, as assumed in the previous section. Thus, if the message is sent between two processes mapped onto different nodes, the message has to be scheduled according to the TTP protocol. Several messages can be packaged together in the data field of a

Figure 4.3: Scheduling Example

frame. The number of messages that can be packaged depends on the slot length corresponding to the node. The effective time spent by a message  $\mathbf{m_i}$  on the bus is  $t_{m_i} = b_{S_i}/T$ , where  $b_{S_i}$  is the length of the slot  $S_i$  and T is the transmission speed of the channel. Therefore, the communication time  $t_{m_i}$  does not depend on the bit length  $b_{m_i}$  of the message  $\mathbf{m_i}$ , but on the slot length corresponding to the node sending  $m_i$ .

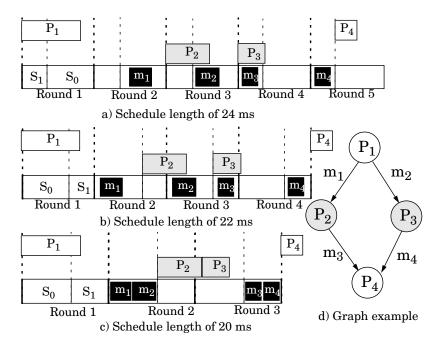

The important impact of the communication parameters on the performance of the application is illustrated in Figure 4.3 by means of a simple example.

In Figure 4.3d we have a process graph consisting of four processes  $P_1$  to  $P_4$  and four messages  $m_1$  to  $m_4$ . The architecture consists of two nodes interconnected by a TTP channel. The first node,  $N_0$ , transmits on the slot  $S_0$  of the TDMA round and the second node,  $N_1$ , transmits on the slot  $S_1$ . Processes  $P_1$  and  $P_4$

are mapped on node  $N_0$ , while processes  $P_2$  and  $P_3$  are mapped on node  $N_1$ . With the TDMA configuration in Figure 4.3a, where the slot  $S_1$  is scheduled first and slot  $S_0$  is second, we have a resulting schedule length of 24 ms. However, if we swap the two slots inside the TDMA round without changing their lengths, we can improve the schedule by 2 ms, as seen on Figure 4.3b. Further more, if we have the TDMA configuration in Figure 4.3c where slot  $S_0$  is first, slot  $S_1$  is second and we increase the slot lengths so that the slots can accommodate both of the messages generated on the same node, we obtain a schedule length of 20 ms which is optimal. However, increasing the length of slots does not necessarily improve a schedule, as it delays the communication of messages generated by other nodes.

In the next two sections our goal is to synthesize the local schedule table of each node and the MEDL of the TTP controller for a given order of slots in the TDMA round and given slot lengths. The ordering of slots and the optimization of slot lengths will be discussed in Section 4.2.3.

#### 4.2.1 SCHEDULING OF MESSAGES WITH THE TTP

Given a certain bus access scheme, which means a given ordering of the slots in the TDMA round and fixed slot lengths, the CPG has to be scheduled with the goal to minimize the worst case execution delay. This can be performed using the algorithm ListScheduling (Figure 4.1) presented in Section 4.1.1. Two aspects have to be discussed here: the planning of messages in predetermined slots and the impact of this communication strategy on the priority assignment.

The function ScheduleMessage in Figure 4.4 is called in order to plan the communication of a message m, with length  $b_m$ , generated on  $Node_m$  and which is ready to be transmitted at TimeReady. ScheduleMessage returns the first round and the corresponding slot (the slot corresponding to  $Node_m$ ) which can host the message. In Figure 4.4 RoundLength is the length of a

```

ScheduleMessage (TimeReady, b<sub>m</sub>, Node<sub>m</sub>)

-- the slot in which the message has to be sent

Slot=the slot assigned to Nodem

-- the first round which could be a candidate

Round= | TimeReady / RoundLength |

-- is the right slot in this round already gone?

if time_ready - Round * RoundLength > start<sub>Slot</sub> then

-- if yes, take the next round

Round = Round + 1

end if

-- is enough space left in the slot for the message?

while b_m > b_{Slot} - b_{occupied} do

-- if not, take the next round

Round = Round + 1

end while

-- return the right round and slot

return (Round, Slot)

end ScheduleMessage

```

Figure 4.4: Message Scheduling

TDMA round expressed in time units (in Figure 4.5, for example, RoundLength=18 ms). The first round after TimeReady is the initial candidate to be considered. For this round, however, it can be too late to catch the right slot, in which case the next round is selected. When a candidate round is selected we have to check that there is enough space left in the slot for our message ( $b_{occupied}$  represents the total number of bits occupied by messages already scheduled in the respective slot of that round). If no space is left, the communication has to be delayed for another round.

With this message scheduling scheme, the algorithm in Figure 4.1 will generate correct schedules for a TTP based architecture, with guaranteed worst case execution delays. However, the quality of the schedules can be much improved by adapting the pri-

ority assignment scheme so that particularities of the communication protocol are taken into consideration.

#### 4.2.2 IMPROVED PRIORITY FUNCTION

For the scheduling algorithm outlined previously we initially used the Partial Critical Path (PCP) priority function [Dob98, Ele98b, Ele00]. PCP uses as a priority criterion the length of that part of the critical path corresponding to a process  $P_i$  which starts with the first successor of  $P_i$  that is assigned to a processor different from the processor running  $P_i$ . The PCP priority function is statically computed once at the beginning of the scheduling procedure.

However, considering the concrete definition of our problem, significant improvements of the resulting schedule can be obtained by including knowledge of the bus access scheme into the priority function. This new priority function will be used by the GetReadyProcess (Figure 4.1) in order to decide which process to select from the list of ready process.

Figure 4.5: Priority Function Example

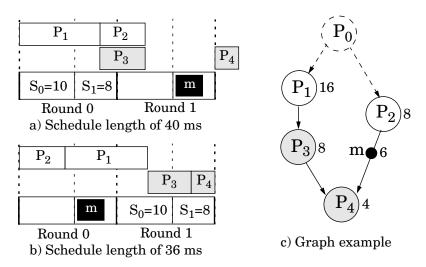

Let us consider the graph in Figure 4.5c, and suppose that the list scheduling algorithm has to decide between scheduling process  $P_1$  or  $P_2$  which are both ready to be scheduled on the same programmable processor. The worst case execution time of the processes is depicted on the right side of the respective node and is expressed in ms. The architecture consists of two nodes interconnected by a TTP channel. Processes  $P_1$  and  $P_2$  are mapped on node  $N_1$ , while processes  $P_3$  and  $P_4$  are mapped on node  $N_0$ . Node  $N_0$  transmits on slot  $S_0$  of the TDMA round and  $N_1$  transmits on slot  $S_1$ . Slot  $S_0$  has a length of 10 ms while slot  $S_1$  has a length of 8 ms. For simplicity we suppose that there is no message transferred between  $P_1$  and  $P_3$ . PCP (see Section 4.1.2) assigns a higher priority to  $P_1$  because it has a partial critical path of 12, starting from  $P_3$ , longer than the partial critical path of  $P_2$  which is 10 and starts from m. This results in a schedule length of 40 ms as depicted in Figure 4.5a. On the other hand, if we schedule  $P_2$  first, the resulting schedule, depicted in Figure 4.5b, is of only 36 ms.

This apparent anomaly is due to the fact that the way we have computed PCP priorities, considering message communication as a simple activity of delay 6ms, is not realistic in the context of a TDMA protocol. Let us consider the particular TDMA configuration in Figure 4.5 and suppose that the scheduler has to decide at t=0, which one of the processes  $P_1$  or  $P_2$  to schedule. If  $P_2$  is scheduled, the message is ready to be transmitted at t'=8. Based on a computation similar to that used in Figure 4.5, it follows that message m will be placed in round  $\lfloor 8/18 \rfloor = 0$ , and it arrives in time to get slot  $S_1$  of that round ( $TimeReady=8 < start_{S1}=10$ ). Thus, m arrives at  $t_{arr}=18$ , which means a delay relative to t'=8 (when the message was ready) of  $\delta=10$ . This is the delay that should be considered for computing the partial critical path of  $P_2$ , which now results in  $\delta+t_{P4}=14$  (longer than the one corresponding to  $P_1$ ).

The obvious conclusion is that priority estimation has to be based on message planning with the TDMA scheme. Such an estimation, however, cannot be performed statically, before scheduling. If we take the same example in Figure 4.5, but consider that the priority based decision is taken by the scheduler at t=5, m will be ready at t'=13. This is too late for m to get into slot  $S_I$  of round 0. The message arrives with round 1 at  $t_{arr}=36$ . This leads to a delay due to the message passing of  $\delta=36-13=23$ , different from the one computed above.

We introduce a new priority function, the modified PCP (MPCP), which is computed during scheduling, whenever several processes are in competition to be scheduled on the same resource. Similar to PCP, the priority metric is the length of that portion of the critical path corresponding to a process  $P_i$  which

```

Lambda(lambda, CurrentProcess)

if CurrentProcess is a message then

slot = slot of node sending CurrentProcess

round = lambda / RoundLength

if lambda - RoundLength * round > start of slot in round

round = next round

end if

while not message fits in the slot of round then

round = next round

end while

lambda = round * RoundLength +

start of slot in round + length of slot

else

lambda = lambda + WCET of CurrentProcess

end if

if lambda > MaxLambda

MaxLambda = lambda

end if

for each successor of CurrentProcess

Lambda(lambda, successor)

end for

return MaxLambda

end Lambda

```

**Figure 4.6:** The Lambda Function

starts with the first successor of  $P_i$  that is assigned to a processor different from  $M(P_i)$ . The critical path estimation starts with time t at which the processes in competition are ready to be scheduled on the available resource. During the partial traversal of the graph the delay introduced by a certain node  $P_j$  is estimated as follows:

$$\delta_{Pj} = \begin{cases} t_{Pj}, \text{ if } P_j \text{ is not a message passing} \\ t_{arr} \text{-}t', \text{ if } P_j \text{ is a message passing} \end{cases}$$

$t^{\prime}$  is the time when the node generating the message terminates (and the message is ready);  $t_{arr}$  is the time when the slot to which the message is supposed to be assigned has arrived. The slot is determined like in Figure 4.4, but without taking into consideration space limitations in slots.

Thus, the priority function MPCP has to be dynamically determined during the scheduling algorithm for each ready process, every time the GetReadyProcess function is activated in order to select a process from the ReadyList. The computation of MPCP is performed inside the GetReadyProcess function and involves a partial traversal of the graph, as presented in Figure 4.6.

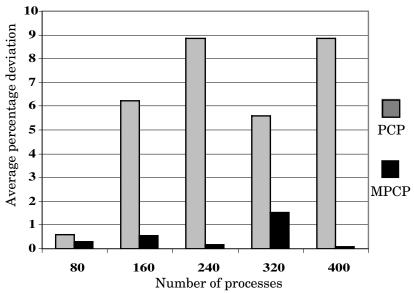

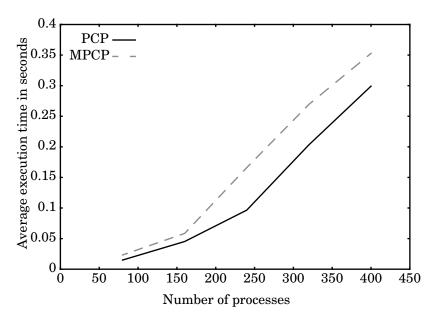

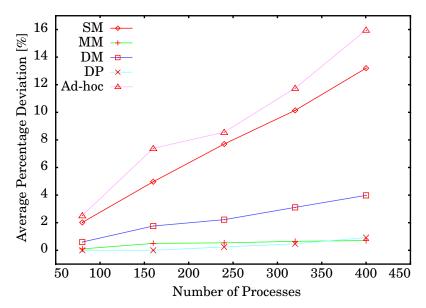

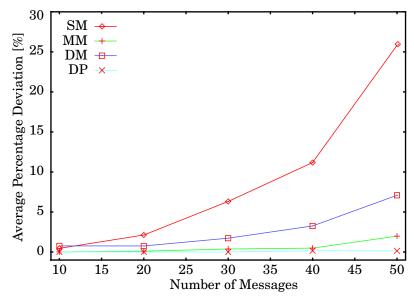

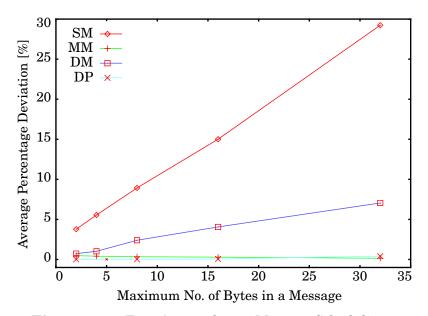

As the experimental results (Section 4.3) show, using MPCP instead of PCP for the TTP based architecture results in an important improvement of the quality of generated schedules, with a slight increase in scheduling time.

#### 4.2.3 Communication Synthesis

In the previous subsections we have shown how the algorithm ListScheduling can produce an efficient schedule for a CPG, given a certain TDMA bus access scheme. However, as shown in Figure 4.3, both the ordering of slots and the slot lengths strongly influence the worst case execution delay of the system.

We first present a heuristic which, based on a greedy approach, determines an ordering of slots and their lengths so that the worst case delay corresponding to a certain CPG is as small as possible.

**Greedy Approaches.** The initial solution, the so called "straightforward" one, assigns in order nodes to the slots  $(Node_{Si}=N_i)$  and fixes the slot length  $length_{Si}$  to the minimal allowed value, which is equal to the length of the largest message generated by a process assigned to  $Node_{Si}$ . The algorithm

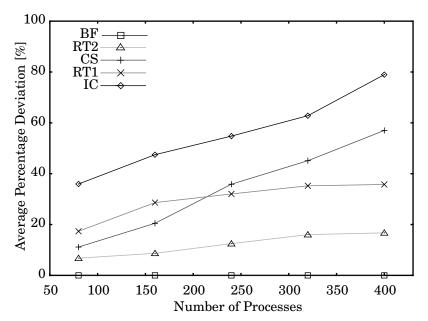

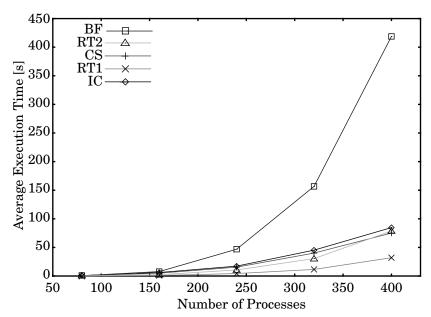

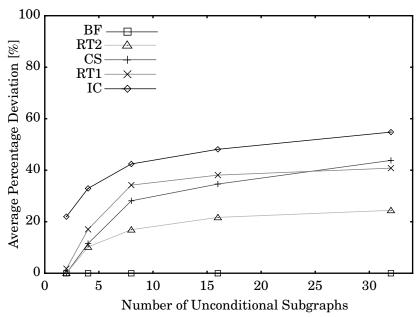

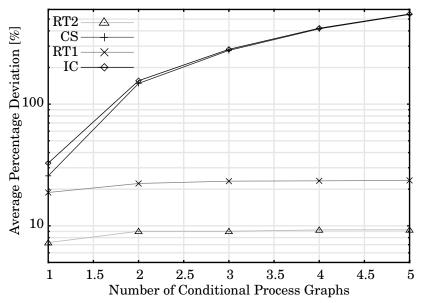

```