## Modeling and simulation of the TTEthernet communication protocol

Alexander Zafirov

Kongens Lyngby 2013 IMM-M.Sc.-2013

Technical University of Denmark Informatics and Mathematical Modelling Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk www.imm.dtu.dk IMM-M.Sc.-2013 I dedicate this master thesis project to my grandfather Alexander Velikov(1927-2011).

## Abstract

Embedded systems have countless application areas - household electronics, computer networks, medical equipment, aircraft controllers, etc. Their responsibility varies depending on the system they are integrated in. Hard-real time systems are the ones where computing the correct result by a task and it meeting its deadline is of great importance. The correctness of these results depends also on the time when these are produced. By extending the list of constrains to the application with high reliability and fault tolerance, the outline of the safety-critical systems characteristics is given. Nowadays complex embedded real-time systems are implemented using distributed architectures, composed of heterogeneous processing elements interconnected using communication networks.

The master thesis objective is to model and simulate the TTEthernet - targeted to distributed safety-critical real-time systems. A TTEthernet network is composed of a set of clusters. Each cluster consists of a set of End Systems (ESes) interconnected by links and Network Switches (NSes). The links are full duplex, allowing thus communication in both directions. The protocol has three traffic classes of different timing criticality: Time-Triggered (TT), Rate-Constrained (RC) and Best Effort (BE). Time-Triggered(TT) messages are the ones with highest priority and take precedence over other messaging types in the network. TT communication is done through offline scheduling of static scheduling tables i.e. messages are sent at predefined periods of time. RC transmission has less priority than a TT one and is executed whenever no time-triggered communication is present. RC provides bounded end-to-end latency and delay limitation. BE messages are the ones with lowest critical level - thus least priority. They do not provide any timing constraints or guarantees that a message will be received. This makes them less reliable for tasks with high temporal requirements. TTEthernet is compliant with ARINC 664p7 [afd09] which defines the concept of virtual links. TTEthernet implements them as logical point-to-point connections in the network. They create "tree" structures with an End System as the root node and a set of End Systems each of which defined as a leaf node. These structures are used to route frames from the root to the leafs. Each virtual link carries a single message.

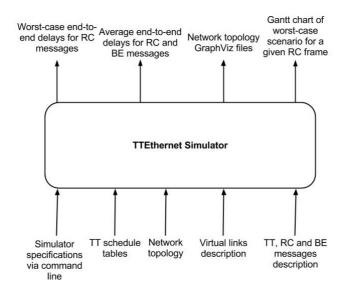

The result of the work done is the creation of a simulator. This tool takes as input the network topology, set of messages in the system and multiple simulation characteristics via command line. The output files are a comma separated value (CSV) file containing the worst-case and average delays, a GraphViz file presenting the network topology from each virtual link's perspective and a Joint Photographic Experts Group (JPEG) file showing a Gantt chart with the scenario that led to the worst-case end-to-end delay for a predefined frame.

In order to evaluate the working of the simulator, different tests were done both with artificial and real world examples. The artificial ones were presented as ten test cases. The real world examples were based on NASA's Orion Crew Exploration Vehicle, represented as a topology in two versions - a simple and an enhanced one. The output produced by the simulator was used for different purposes. In the case of Orion it determined the appropriateness of a given topology for the needs that the system presents. In the other test cases - the steady-state was sought with respect to the amount of simulation performed. Finally, the output was compared to previously performed analysis in the form of a discussion which gave a broader understanding of the relation analysissimulation.

# Acknowledgements

First and foremost I want to thank Paul Pop for being a great supervisor. The communication that we had throughout the master thesis project was always timely, concise and valuable.

I would also like to thank Domitian Tamas-Selicean for his extensive support. His feedback - both technical and theoretical - helped me numerous times get pass difficult problems.

Lastly, I would like to thank my family and friends for the being there for me when I needed them most. I love you!

## Contents

| Abstract ii |               |                                      |     |  |

|-------------|---------------|--------------------------------------|-----|--|

| A           | cknov         | vledgements                          | v   |  |

| Li          | st of         | Figures v                            | iii |  |

| 1           | Intr          | oduction                             | 1   |  |

|             | 1.1           | Databus                              | 3   |  |

|             | 1.2           | Communication protocols              | 3   |  |

|             | 1.3           | Thesis objectives                    | 7   |  |

|             | 1.4           | Thesis structure                     | 7   |  |

| <b>2</b>    | $\mathbf{TT}$ | Ethernet                             | 9   |  |

|             | 2.1           | Background and Definition            | 9   |  |

|             | 2.2           | Virtual links                        | 11  |  |

|             |               | 2.2.1 Virtual link isolation         | 11  |  |

|             |               | 2.2.2 Virtual link scheduling        | 13  |  |

|             | 2.3           | Architecture                         | 14  |  |

|             | 2.4           | Traffic classes                      | 15  |  |

|             | 2.5           | Protocol operation                   | 17  |  |

|             |               | 2.5.1 Time-Triggered Communication   | 18  |  |

|             |               | 2.5.2 Rate Constrained Communication | 19  |  |

|             |               | 2.5.3 Integration Policies           | 20  |  |

|             | 2.6           |                                      | 21  |  |

|             | 2.7           | Fault-tolerance                      | 23  |  |

|             | 2.8           | Summary                              | 26  |  |

| 3  | Mo             | leling and Simulation                           | <b>27</b> |

|----|----------------|-------------------------------------------------|-----------|

|    | 3.1            | System                                          | 27        |

|    | 3.2            | Model                                           | 28        |

|    |                | 3.2.1 Verification and Validation               | 30        |

|    | 3.3            | Simulation                                      | 32        |

|    |                | 3.3.1 Selecting input probability distributions | 32        |

|    |                | 3.3.2 Random Number Generation                  | 33        |

|    |                | 3.3.3 Output Data Analysis                      | 34        |

|    | 3.4            | Simulation paradigms                            | 35        |

|    | 0              | 3.4.1 DES                                       | 36        |

|    |                |                                                 |           |

| 4  | $\mathbf{Sim}$ | ulator design and implementation                | 39        |

|    | 4.1            | Requirements                                    | 39        |

|    | 4.2            | Simulator design                                | 40        |

|    | 4.3            | Implementation                                  | 44        |

|    |                | 4.3.1 Activity-oriented simulator               | 58        |

|    |                | 4.3.2 Event-oriented simulator                  | 60        |

| 5  | Tost           | ing and Evaluation                              | 65        |

| J  | 5.1            |                                                 | 65        |

|    | $5.1 \\ 5.2$   | Evaluation                                      | 68        |

|    | 0.2            |                                                 | 00        |

| 6  | Con            | clusion                                         | 77        |

|    | 6.1            | Future work                                     | 78        |

| A  | Арр            | oendix A                                        | 81        |

| в  | App            | oendix B                                        | 87        |

| Bi | bliog          | raphy                                           | 91        |

# List of Figures

| 1.1  | J. Rushby. "Generic Bus" Figure. [Rus01], 5p.                       | 4  |

|------|---------------------------------------------------------------------|----|

| 1.2  | J. Rushby. "Interconnect Bus" Figure. [Rus01], 6p                   | 4  |

| 1.3  | J. Rushby. "Star Interconnect" Figure. [Rus01], 7p                  | 5  |

| 1.4  | J. Rushby. "Spider Interconnect" Figure. [Rus01], 8p                | 6  |

|      |                                                                     |    |

| 2.1  | "Full-Duplex, Switched Ethernet Example" Figure. [Eng05], 12p.      | 10 |

| 2.2  | "Determinism context in Ethernet networks depends of the appli-     |    |

|      | cation (max. sampling rate) and the approach to system design       |    |

|      | asynchronous (coordination and synchronization among functions      |    |

|      | is conducted at higher layers) or synchronous (control of timing    |    |

|      | and synchronization at network level)." Figure. [Pla09a], 4p.       | 11 |

| 2.3  | "Format of Ethernet Destination Address in AFDX Network."           |    |

|      | Figure. [Pla05], 12p                                                | 12 |

| 2.4  | "Packet Routing Example." Figure. [Pla05], 11p                      | 12 |

| 2.5  | "Three Virtual Links Carried by a Physical Link." Figure. [Pla05],  |    |

|      | 14p                                                                 | 13 |

| 2.6  | "Allowable BAG Values." Table. [Pla05], 14p                         | 13 |

| 2.7  | "Virtual Link Scheduling." Figure. [Pla05], 15p.                    | 14 |

| 2.8  | Figure. [Pla05], 15p                                                | 14 |

| 2.9  | "The TTE<br>thernet synchronization topology has four levels." Fig- |    |

|      | ure. [Pla09a], 15p                                                  | 15 |

| 2.10 |                                                                     | 16 |

| 2.11 | "Relation of TTEthernet to existing communication standards."       |    |

|      | Figure. [TSPS12], 10p                                               | 16 |

| 2.12 | "TTEthernet includes TT, RC and BE messages." Figure. [Pla09a],     |    |

|      | 11p                                                                 | 17 |

| 2.13 | "TT and RC message transmission example." Figure. [TSPS12],         |    |

|      | 4p                                                                  | 18 |

|            | "Multiplexing two RC frames." Figure. [TSPS12], 5p                   | 19         |

|------------|----------------------------------------------------------------------|------------|

| 2.15       | "Integration Methods for High-Priority (H) and Low-Priority (L)      | 20         |

| 0.16       | Traffic." Figure. [TSPS12], 192p                                     | 20         |

| 2.16       | I V 0 [ ], I                                                         | 22         |

|            | "Initial TT schedule" Figure. [TSPS12], 6p                           | 23         |

| 2.18       | · · · · · · · · · · · · · · · · · · ·                                | 23         |

| 2.19       |                                                                      | 23         |

| 2.20       |                                                                      | 24         |

| 2.21       | "Receive Processing of Ethernet Frames." Figure. [Pla05], 13p. $\ .$ | 25         |

| 2.22       | "TTEthernet provides implicit fault tolerance mechanisms." Fig-      |            |

|            | ure. [Pla09b], 7p                                                    | 25         |

| 3.1        | "Computer Networking - LAN Networking". Digital image. Ac-           |            |

|            | cessed 16 August 2013                                                | 28         |

| 3.2        | "Ways to study a system". Figure. [LK99], 4p                         | 29         |

| 3.3        | "Construction of a model". Figure. [BCNN00]                          | 30         |

| 3.4        | "Types of simulations with regard to Output Analysis". Figure.       | 34         |

| 3.5        | "Transient and steady-state density functions". Figure. [LK99] .     | 35         |

| 3.6        | "Fixed-increment time advance". Figure. [LK99], 9p                   | 36         |

| 3.7        | "Next-event time-advance approach". Figure. [LK99], 93p              | 37         |

| 4.1        | Abstract representation of the TTEthernet simulator                  | 41         |

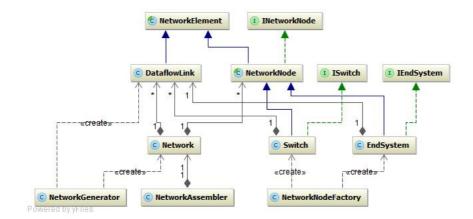

| 4.2        | Simulator. UML diagram.                                              | 45         |

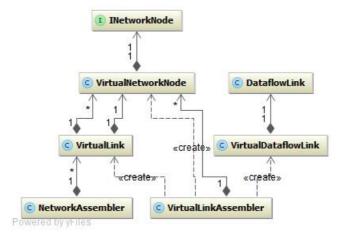

| 4.3        | Network. UML diagram.                                                | 46         |

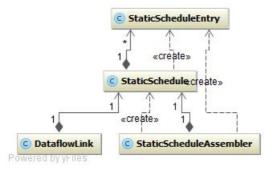

| 4.4        | Dataflow links use StaticSchedule. UML diagram.                      | 46         |

| 4.5        | Virtual links. UML diagram.                                          | 47         |

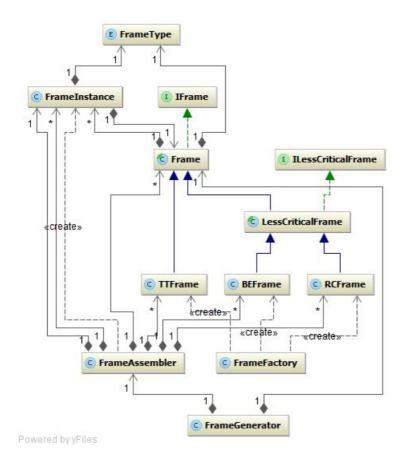

| 4.6        | Messages. UML diagram.                                               | 48         |

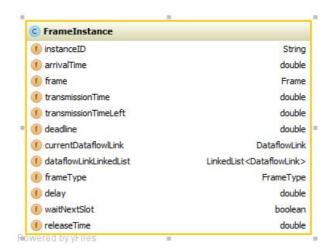

| 4.7        | Frame instance                                                       | 49         |

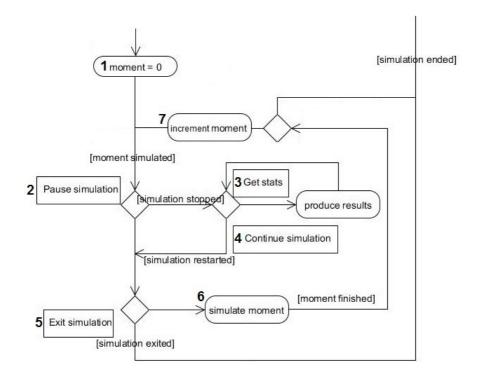

| 4.8        | Stepwise simulation. Activity diagram.                               | $50^{49}$  |

| 4.8<br>4.9 | Simulation initialization. Activity diagram.                         | $50 \\ 51$ |

|            |                                                                      | $51 \\ 52$ |

|            | Main simulation loop. Activity diagram.                              |            |

|            | Stepwise simulator. UML diagram.                                     | 53<br>57   |

|            | Strategy design pattern for Integration policy. UML diagram.         | 57         |

| 4.13       | Simulate moment. Activity-oriented implementation. Activity          | 50         |

|            | diagram.                                                             | 59         |

| 4.14       | A frame instance finished transmitting. Activity-oriented imple-     | 50         |

|            | mentation. Activity diagram.                                         | 59         |

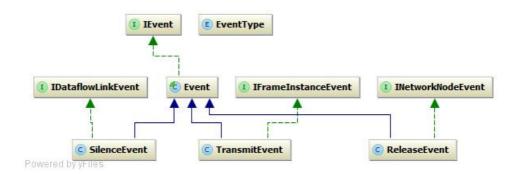

|            | Event. Class diagram.                                                | 61         |

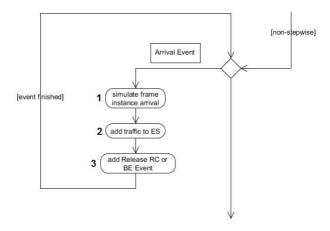

|            | Arrival event in event-oriented implementation. Activity diagram.    | 61         |

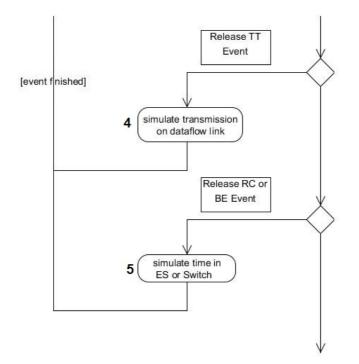

| 4.17       | Release of TT event and RC or BE event in event-oriented im-         |            |

|            | plementation. Activity diagram.                                      | 62         |

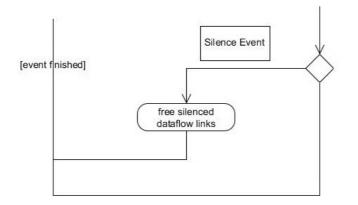

|            | Finish event in event-oriented implementation. Activity diagram.     | 63         |

| 4.19       | Silence event and end of simulation. Activity diagram                | 64         |

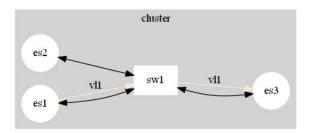

| 5.1  | Network with vl1                                                                      |

|------|---------------------------------------------------------------------------------------|

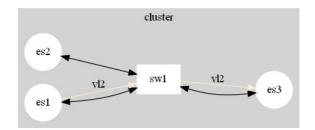

| 5.2  | Network with vl2                                                                      |

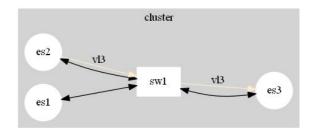

| 5.3  | Network with vl3                                                                      |

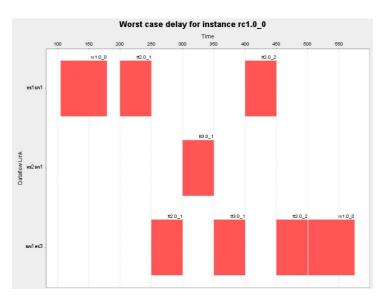

| 5.4  | Progression of time on the dataflow links                                             |

| 5.5  | Percentile difference between the 1000, 1500, 2000, 2500, 3000,                       |

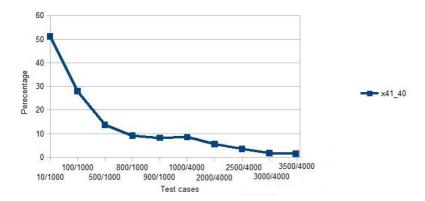

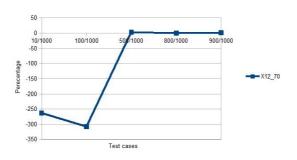

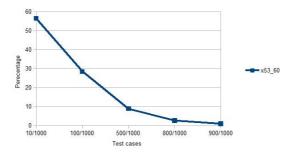

|      | $3500$ with respect to $4000$ Simulation runs $\ldots \ldots \ldots \ldots \ldots 72$ |

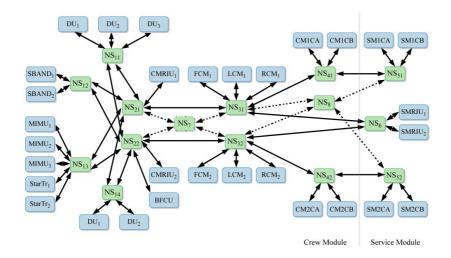

| 5.6  | Orion topology                                                                        |

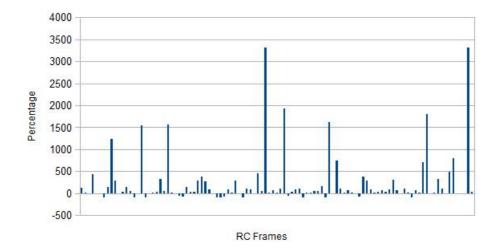

| 5.7  | Percentage difference between the two Orion test cases 75                             |

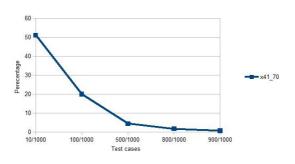

| A.1  | Results for test case 1                                                               |

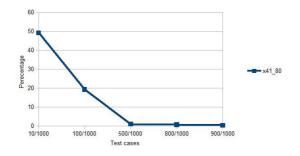

| A.2  | Results for test case 2                                                               |

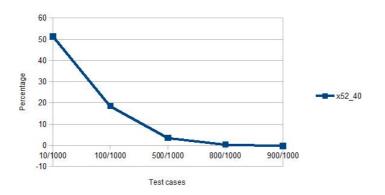

| A.3  | Results for test case 3                                                               |

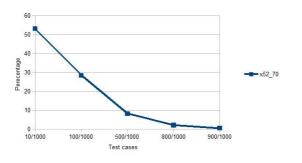

| A.4  | Results for test case 4                                                               |

| A.5  | Results for test case 5                                                               |

| A.6  | Results for test case 6                                                               |

| A.7  | Results for test case 7                                                               |

| A.8  | Results for test case 8                                                               |

| A.9  | Results for test case 9                                                               |

| A.10 | Results for test case 10                                                              |

## CHAPTER 1

## Introduction

The term "embedded systems" describes systems that repeatedly extract and analyze information from sensors, generating output sent to actuators. They are also known as closed-loop control systems. There are various ways one can classify them - according to their cost, performance, safety, dependability etc.

Hard-real time systems have the highest demand on the programs they utilize due to the nature of their domain. Applications executing on such systems should work in a timely manner - any deadlines that are not met lead to catastrophic consequences loss of data, financial resources or potential threat to human life. Systems with such characteristics are further refined as safety-critical. An example one can point out are applications such as fly- and drive-by-wire where there are no direct connections between a pilot operating the control system of an aircraft and its control surfaces. Such an environment poses multiple requirements - ultra-high reliability (e.g. minimum delay of a command send from the aircraft control to its surfaces), fault tolerance, extensive redundancy.

To address these and other demands, separation of the communication in multiple types is needed. Subsequently, two of the approaches developed to deal with this in real-time systems ([Kop11]) are **event-triggered** and **time-triggered** ([Suel2]). The former describes the action of triggering a signal upon the occurrence of a specific event. This implies a dynamic strategy of dealing with events. The later is managed by the progression of time. Each communication that hap-

pens is a predefined static periodic event. A time-triggered system interacts with the world according to an internal schedule, whereas an event-triggered system responds to stimuli that are outside its control.

The term mixed-criticality ([BBB<sup>+</sup>09]) applications denotes the integration of both approaches onto the same system. It refers to those applications that comprise non-critical and critical traffic with different Safety-Integrity Levels (SIL). To achieve this they are divided through temporal and spatial separation. The functionality of mixed-criticality applications is implemented on top of an integrated structure of interconnected heterogeneous processing elements.

A setting as complex as an aircraft encompasses another class of embedded systems - distributed systems. They were initially devised as being **federated**. This definition implies that each applications in the system (e.g. autopilot) comprises of a fault-tolerant embedded control system that connects to others of its kind through minor interconnections. This is also known as partitioning ([Rus99]). The newer applications adapt the approach of **integrated** solutions, where resources are shared throughout multiple applications. The trade-off between both approaches is as follows: in the case of federated architectures there are higher expenses for replicating the systems a great amount of times as well as protection against fault propagation. On the other hand, integrated solutions lower the costs for integrating the applications but introduce risk of cascading failures. Both architectures represent the safety-critical core of the applications built on top of them. Deciding how to implement them and what services to provide them with, are major key points in the construction and certification of safety-critical embedded systems.

The two systems designs approaches - time-triggered and event-triggered - find application in different areas. The time-triggered approach is generally preferred for integrated safety-critical systems. An integrated system brings different applications together - whereas a safety-critical system keeps them apart. This is a reference to the previously denoted term partitioning. It allows single applications to be "deconstructed" into smaller components that can be developed to different safety levels. Also although the purpose of partitioning is to exclude fault propagation, it has the added benefit that it promotes composability.<sup>1</sup> Partitioning and composability concern the predictability of the resources and services perceived by the clients (applications and their subfunctions) of an architecture. One of predictability's two dimensions is value - logically correct behavior. The other is time - predictable rate of delivery, latency and jitter of services. Especially in context of fault-tolerant systems temporal predictability is difficult to achieve in event-triggered architectures. This makes

<sup>&</sup>lt;sup>1</sup>A composable design is one in which individual applications are unaffected by the choice of the other applications with which they are integrated.

time-triggering the only option for safety-critical systems.

### 1.1 Databus

One of the primary architectural components is the bus (databus). It can be a physical or logical entity (communication protocol) and is used for control and transmission of communication across the network. Buses such as Ethernet resolve contention probabilistically and therefore can provide only probabilistic guarantees of timely access. Thus they give no assurance at all in the presence of faults. Buses for embedded systems such as CAN, LonWorks, or Profibus (Process Field Bus) use various priority, preassigned slot or token schemes to resolve contention deterministically. Time-triggered buses provide static preallocation of communication bandwidth in the form of a global schedule - each node knows the schedule. It therefore knows when it is allowed to send messages and when it should expect to receive them. This means gives the benefit of resolving contention at design time (i.e. as the schedule is constructed), rather than runtime. This allows for thorough assessment of the impact of the schedule on the system. Because all communication is time-triggered by the global schedule there is no need to attach source or destination addresses to messages sent over the bus each node knows the sender and intended recipients of each message by virtue of the time at which it was sent. Time-triggered operation provides efficiency, determinism, and partitioning.

### **1.2** Communication protocols

Here are the architectures of two avionics and two automobile communication protocols in the interest of deducing principles common to all of them, the main differences in their design choices, and the trade-offs made. On one hand we have the avionics buses the Honeywell SAFEbus ([HD93]) and the SPIDER protocol ([MGPM04]). On the other - the automobile buses Time-Triggered Architecture (TTA) ([KB03]) and FlexRay ([SJ08]). All four of the considered examples are primarily time-triggered ([PSG<sup>+</sup>11]). This is a fundamental design choice that influences many aspects of their architectures and mechanisms and sets them apart from event-triggered buses such as Controller Area Network (CAN), Byteflight and LonWorks.

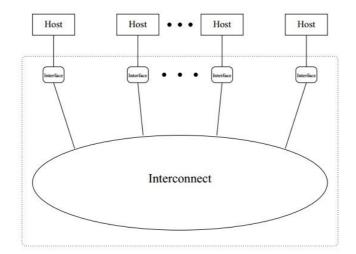

Figure 1.1 depicts a bus interconnect topology similar the one utilized by SAFEbus. The Bus Interface Units (BIUs) are duplicated and the interconnect bus is quad-

Figure 1.1: J. Rushby. "Generic Bus" Figure. [Rus01], 5p.

redundant. Features like clock synchronization, message scheduling and transmission functions are implemented on SAFEbus main unit - the BIU. The access control to the interconnect is done by the bus guardian of BIU's partner. Every Bus Interface Unit of a pair drives a different pair of interconnect buses. It is, however, able to read all four of them. The interconnect buses, on the other hand, are composed each of two data lines and one clock line.

Figure 1.2: J. Rushby. "Interconnect Bus" Figure. [Rus01], 6p.

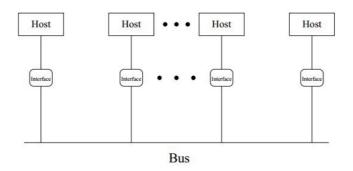

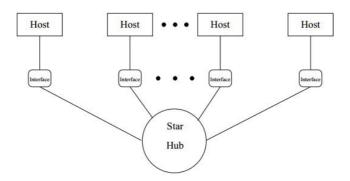

There are two types of implementation of a Time-Triggered Architecture - the currently used TTA-bus (a bus interconnect topology similar to that shown in Figure 1.2) and the next generation TTA-star (a star interconnect topology such as the one in Figure 1.3). Both designs have the same interfaces (also

called controllers), which implement the TTP/C protocol - the heart of TTA. It is responsible for clock synchronization, message sequencing and transmission functions. In a TTA-bus each controller drives the buses through a bus guardian, whereas in a TTA-star implementation the guardian functionality is carried out in the central hub. TTA-star provides a setup for distributed configurations where subsystems are connected by hub-to-hub links.

Figure 1.3: J. Rushby. "Star Interconnect" Figure. [Rus01], 7p.

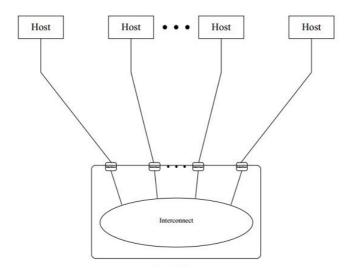

The SPIDER interconnect is composed of active elements called Redundancy Management Units (RMUs). Its topology can be organized either as shown in Figure 1.4, where the RMUs and interfaces (the BIUs) form part of a centralized hub, or as in Figure 1.3, where the RMUs form the hub, or similar to Figure 1.1, where the RMUs provide a distributed interconnect. The lines connecting hosts to their interfaces are optical fiber, and the 12 whole system beyond the hosts (i.e., optical fibers and the RMUs and BIUs) is called the Reliable Optical Bus (ROBUS). Clock synchronization and other services of SPIDER are achieved by distributed algorithms executed among the BIUs and RMUs.

FlexRay can use either an "active" star topology similar to that shown in Figure 1.3, or a "passive" bus topology similar to that shown in Figure 1.2. In both cases, duplication of the interconnect is optional. Each interface f (communication controller) drives the lines to its interconnects through separate bus guardians located with the interface. As with TTA-star, FlexRay can also be deployed in distributed configurations in which subsystems are connected by hub-to-hub links.

In the context of communication protocols implementing the time-triggered architecture, the master thesis takes a closer look at TTEthernet (see chapter 2). This network protocol supports safety-critical applications of mixedcriticality character. It enables interconnection of heterogeneous processing elements in hard-real time safety-critical distributed embedded systems. This is

Figure 1.4: J. Rushby. "Spider Interconnect" Figure. [Rus01], 8p.

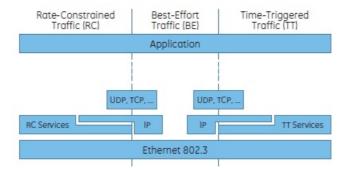

done through the management of three traffic classes - Time-Triggered (TT), Rate-Constrained (RC) and Best Effort (BE). Time-Triggered(TT) messages are the ones with highest priority. Because they have the highest level of criticality, they take precedence over other messaging types in the network. TT communication is done through offline scheduling of static scheduling tables i.e. messages are sent at predefined periods of time. This type of message exchange is most suitable for the construction of deterministic distributed systems where the operation of each element can be specified with high precision.

Event-Triggered communication presents two types of traffic in TTEthernet -Rate-Constrained(RC) and Best Effort(BE). RC messaging is next in the criticality scale of after TT. Thus an RC transmission has less priority than a TT one and is executed whenever no time-triggered communication is present. RC provides bounded end-to-end latency and delay limitation.

BE messages are the ones with lowest critical level - thus least priority. They cannot provide any timing constraints or guarantees that the message will be received at all because they are executed whenever no other communication is present. This, of course, makes them less reliable and useful for tasks with high temporal requirements.

To utilize a "mixed-criticality" application on a single system and enable the transmission of all three classes two key components are needed - spatial and temporal separation. Spatial separation is done through the concept of virtual links. As introduced in ARINC 664p7, virtual links represent logical point-topoint connections that create "tree-like" structures in the network - a single end system as the root node and one or more end systems as leaf nodes. Temporal separation, on the other hand, is achieved in two ways depending on the messages being transmitted. One is the above mentioned static preallocation of bandwidth (offline scheduling). It is used in case of TT communication. If the messages are of RC type, separation is provided through bandwidth allocation. With its fault-tolerance design, TTEthernet comprises various capabilities like redundancy, scalability and multiple fault containment.

#### **1.3** Thesis objectives

The goal of the master thesis project is to develop a simulator based TTEthernet protocol. The simulator has to be fast and accurate. The requirements for the simulator are:

- model the two simulation paradigms action- and event-oriented

- model all the three integration policies (conflict resolution mechanisms) timely block, shuffling and preemption

- determine the average end-to-end delays for all BE and RC messages and the worst-case end-to-end communication delays for the RC messages

- compare and evaluate results from simulation to an existing analysis presented in a paper

- simulator should be designed and implemented so that it can be used inside an optimization loop

### 1.4 Thesis structure

The structure master thesis report is as follows:

• Chapter 1 makes an introduction to the topic of protocols for embedded systems by briefly comparing the characteristics of multiple protocols. It describes the goals and the motivation behind the project.

- Chapter 2 presents the theory used throughout the project with regards to Time-Triggered Ethernet.

- Chapter 3 describes the process of simulation and modeling, the various types of simulations that can be performed and the appropriateness of each one with regards to the master thesis project. It must be noted that the purpose of chapters 2 and 3 is not to educate the reader or repeat the numerous textbooks written in the field. It is intended to support and clarify the decisions made during the implementation process.

- Chapter 4 focuses on the development of two simulators following the action and event-driven paradigms. It gives a detailed view of their common features as well as the differences they have with respect to the implementation, performance and development issues.

- **Chapter 5** reflects on the verification of the simulators correctness and the evaluation of the output data.

- The thesis report completes with **chapter 6** which provides conclusions in the form of a general overview of the theory and the achieved results that were presented. It also gives a description of the possible future extensions.

## Chapter 2

# TTEthernet

The following chapter presents TTEthernet in detail. It is a protocol that interconnects heterogeneous processing elements in hard-real time safety-critical distributed systems. The chapter is divided into sections that describe the background of TTEthernet, the architecture model that it supports, its actual operation, scheduling policies and fault-tolerance techniques that it implements. It also provides an example of the protocol's workflow. Finally, a short summary presents TTEthernet's key features.

### 2.1 Background and Definition

TTEthernet has multiple characteristics, which will be described step-wise in this section. Firstly, TTEthernet is based on IEEE 802.3 Ethernet standard. This means that is supports communication between applications over heterogeneous media. The problem with Ethernet is that it is implemented with half-duplex switching, thus if a message collides with another transmission it is resent after a certain time period depending on the back-off strategy used. No matter how small, the possibility that messages will collide each time still exists. Subsequently these collisions result in unbounded transmission times.

To address these issues, TTEthernet is also made compliant with the ARINC

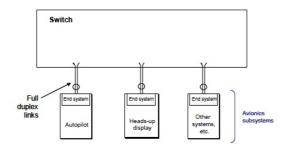

Figure 2.1: "Full-Duplex, Switched Ethernet Example" Figure. [Eng05], 12p.

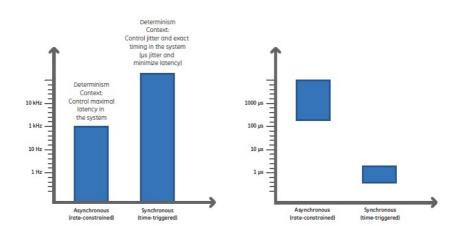

664p7 (see [afd09]) protocol - a full-duplex switched Ethernet with predictable event-triggered communication (see Figure 2.1). The full-duplex mechanism does away with frame collisions but introduces a new threat to the protocol congestion. In order to handle it and make the protocol congestion free, there should be control over the message transmissions. This is directly related to the determinism in TTEthernet. The protocol has predictable operation achieved by a mixed asynchronous/synchronous approach (see Figure 2.2). The asynchronous approach is described in ARINC 664, where bandwidth partitioning is done through rate-constrained communication. Also maximum latency in the system is controlled. The synchronous approach on the other hand manages jitter and has a strict time base - implements time-triggered messaging. It is presented in the SAE AS6802 standard which is a fault-tolerant self-stabilizing synchronization strategy.

The ARINC 664p7 protocol also introduces the concept of virtual links ([ASBCH13]). They represent logical point-to-point connections in the network. Virtual links provide one of the key features needed to implement mixed-criticality applications - spatial separation. A thorough discussion on virtual links can be found in the follow up subsection.

As a further extension to event-triggered communication of ARINC 664p7, TTEthernet provides a static pre-scheduled time-triggered messaging. This augmentation makes the protocol perfect for networks implemented in highly critical hard real-time systems, where deadlines must always be respected. To summarize, TTEthernet is defined as a synchronous, deterministic and congestion free.

Figure 2.2: "Determinism context in Ethernet networks depends of the application (max. sampling rate) and the approach to system design asynchronous (coordination and synchronization among functions is conducted at higher layers) or synchronous (control of timing and synchronization at network level)." Figure. [Pla09a], 4p.

### 2.2 Virtual links

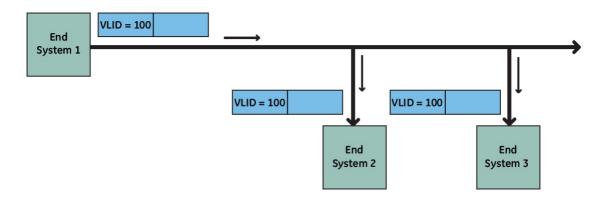

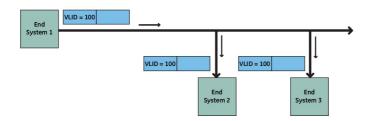

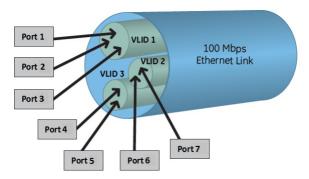

Virtual links are used to route frames from a sender to one or multiple receivers. In TTEthernet the Virtual Link ID (VLID) is of size 16 bits and type unsigned integer. Traffic is navigated through the network based on the resulting 48 bit destination address (see Figure 2.3).

Because switches in the TTEthernet network are configured so that they redirect messages to one or multiple links and because end systems can only have a single VLID, virtual link connections create structures that resemble "trees" with an end system as the root node and a set of end systems each of which defined as a leaf node. Figure 2.3 depicts the routing of a frame from end system 1 with VLID 100 through the network to the designated communication ports in end systems 2 and 3.

#### 2.2.1 Virtual link isolation

As previously described virtual links are logical connections between two end systems which provide spatial separation among traffic of different character i.e. critical and non-critical. Figure 2.5 shows that any given physical link can

Figure 2.3: "Format of Ethernet Destination Address in AFDX Network." Figure. [Pla05], 12p.

Figure 2.4: "Packet Routing Example." Figure. [Pla05], 11p.

contain one or more virtual links, which in turn transport frames to a single or multiple destination ports.

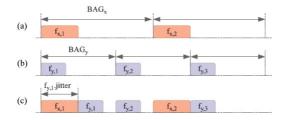

In order to isolate the traffic being transmitted and to make sure that no interference between communication of different messages is possible, TTEthernet limits the frame rate and size that passes through the virtual links. Thus each frame is supplied with a Bandwidth Allocation Gap (BAG) and a Lmax value. BAG is the minimal time interval (in ms) between the transmission of two frames in the network. Lmax is the maximum size (in bytes) one frame can have in the given virtual link. Appropriate values for BAG and their matching transmission frequencies are given in Figure 2.6. These parameters are assigned on per-virtual link basis for in each end system.

Figure 2.5: "Three Virtual Links Carried by a Physical Link." Figure. [Pla05], 14p.

| BAG          |        |

|--------------|--------|

| milliseconds | Hz     |

| 1            | 1000   |

| 2            | 500    |

| 4            | 250    |

| 8            | 125    |

| 16           | 62.5   |

| 32           | 31.25  |

| 64           | 15.625 |

| 128          | 7.8125 |

Figure 2.6: "Allowable BAG Values." Table. [Pla05], 14p.

#### 2.2.2 Virtual link scheduling

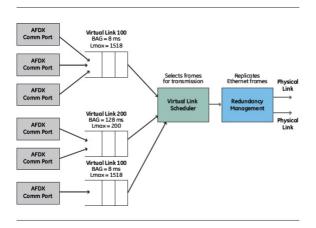

As shown in the previous subsection, communication ports are linked to virtual links. Messages coming from the ports that are to be sent by the end system must follow the scenario depicted in Figure 2.7. First they are wrapped into a TTEthernet frame and placed in a transmission queue. Virtual Link Scheduler (VLS) supervises whether the BAG and Lmax limitations for the given virtual link are respected. It regulates the amount of jitter of the communication by transmitting the traffic passing through it. Some sources of jitter are congestion in the virtual link queues, multiplexing the scheduled frames into the Redundancy Management Unit (RMU) and their actual transmission through the physical links.

The formulas given below determine a bound on the output jitter that every end system must comply with. The first describes the upper bound to the amount of

Figure 2.7: "Virtual Link Scheduling." Figure. [Pla05], 15p.

jitter on the delay that a frame can experience when other frames are scheduled on other virtual links. The second one is limit on the overall jitter of the end system. If these limitations are met by all end systems, the cluster will prove to be "deterministic".

$$\max_{jitter \leq 40 \, \mu s} + \frac{\sum_{j \in \{set of \ VLs\}} (20 + L \max_{j}) \times 8)}{Nbw}$$

$max_jitter \le 500 \mu s$

Figure 2.8: Figure. [Pla05], 15p.

When the VLS passed a frame on, it receives a sequence number and gets replicated by the RMU, if that is needed. The complete frame is then transmitted over the network through the physical link.

#### 2.3 Architecture

The following section presents the architecture of TTEthernet through a simple example that is situated on the "cluster level" in the TTEthernet synchronization topology i.e. there is one synchronization domain and one priority (see Figure 2.9).

| Network Level       | y Synchronization Domains<br>(y. z) Synchronization Priorities            |

|---------------------|---------------------------------------------------------------------------|

| Multi-Cluster Level | One Synchronization Domain<br>× Synchronization Priorities                |

| Cluster Level       | One Synchronization Domain<br>One Synchronization Priority                |

| Device Level        | Synchronization Masters<br>Synchronization Clients<br>Compression Masters |

Figure 2.9: "The TTEthernet synchronization topology has four levels." Figure. [Pla09a], 15p.

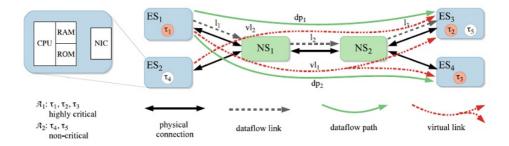

Figure 2.10 shows a cluster containing four end systems  $(ES_1, ES_2, ES_3, ES_4)$ which communicate among themselves through the means of physical links and network switches  $(NS_1, NS_2)$ . The path from one ES to another is called a communication channel and encompasses all the communication media in between. Every ES is supplied with a CPU, RAM, ROM (or some other type of non-volatile memory) and network interface card (NIC) used to identify the ES on the TTE thernet network. Communication in the cluster is implemented as full-duplex and is denoted with solid black bi-directional arrows. Some other characteristics of the cluster are that it is multi-hop i.e. messages can travel through multiple NSes and that TT messages are synchronized per cluster. The Figure 2.9 depicts two applications  $A_1$  and  $A_2$  that have different criticality level tasks. A<sub>1</sub> maps its highly critical tasks  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  onto ES<sub>1</sub>, ES<sub>3</sub> and ES<sub>4</sub> respectively. The non-critical application  $A_2$  places its tasks  $\tau_1$  and  $\tau_4$  on  $ES_1$  and  $ES_4$ . The spatial separation that TTE thernet provides addresses the system's mixed-critically character. In the example below it can happen so that messages sent from task  $\tau_1$  and  $\tau_4$  intersect in a physical connection or a network switch. In this case the virtual links  $vl_1$  and  $vl_1$  are used to isolate critical from non-critical messages. Virtual links consists of multiple dataflow paths which in turn contain uni-directional flow constructs called dataflow links.

Besides the example presented in Figure 2.10 there also exist other topologies such as single cluster with redundant communication channels or cascaded multiclusters implementing a master-slave strategy.

#### 2.4 Traffic classes

As previously noted, TTEthernet implements both event-triggered and timetriggered communication in order to satisfy applications of mixed-criticality

Figure 2.10: "TTEthernet cluster example." Figure. [TSPS12], 3p.

character. This is reflected in the traffic that the protocol generates by creating three categories of messages. Time-Triggered (TT) messages are the ones with highest priority. Because they have the highest level of criticality, they take precedence over other messaging types in the network. TT communication is done through offline scheduling of static scheduling tables i.e. messages are sent at predefined periods of time. This type of message exchange is most suitable for the construction of deterministic distributed systems where the operation of each element can be specified with high precision. Event-Triggered communication presents two types of traffic in TTEthernet - Rate-Constrained (RC) and Best Effort (BE). RC messaging is next in the criticality scale of after TT. Thus an RC transmission has less priority than a TT one and is executed whenever no time-triggered communication is present. RC provides bounded end-to-end latency and delay limitation.

Figure 2.11: "Relation of TTEthernet to existing communication standards." Figure. [TSPS12], 10p.

BE messages are the ones with lowest critical level - thus least priority. They cannot provide any timing constraints or guarantees that the message will be

received at all because they are executed whenever no other communication is present. This, of course, makes them less reliable and useful for tasks with high temporal requirements.

| TT TT | RC BE      | TT  | TT BE           | BE TT      | RC TT      | TT BE      |

|-------|------------|-----|-----------------|------------|------------|------------|

|       | 3 ms cycle |     |                 | 3 ms cycle | <b>+</b>   | 3 ms cycle |

|       | 2 ms cycle |     | 2 ms cycle      | <b>`</b>   | 2 ms cycle | 2 ms cycle |

|       |            | 6 m | s cluster cycle |            |            |            |

Figure 2.12: "TTEthernet includes TT, RC and BE messages." Figure. [Pla09a], 11p.

As already stated both temporal and spatial separation is needed to utilize a "mixed-criticality" application on a single system. The spatial separation is done through the concept of virtual links. Temporal separation is achieved in two ways depending on the messages being transmitted. Offline scheduling is used in case of TT communication. If the transmissions are of RC type, separation is provided through bandwidth allocation.

TTEthernet is a transparent synchronization protocol which enables it to exchange "foreign" types of traffic on the same network. To provide fault-tolerance some part of the devices in that network can be implemented so that they generate synchronization messages.

### 2.5 Protocol operation

Now that the elements of the TTEthernet topology have been presented, this subsection will delve into how the actual transmission of messages takes place. The focus of the example will be critical communication in the protocol i.e. TT and RC messages.

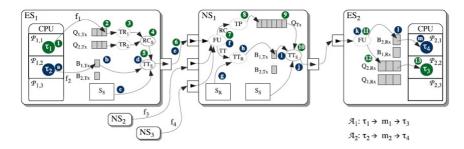

Figure 2.13 presents a cluster consisting of two end systems (ES<sub>1</sub> and ES<sub>2</sub>) and three network switches (NS<sub>1</sub>, NS<sub>2</sub>, NS<sub>3</sub>). The communication channel that will be the focus of this example starts at ES<sub>1</sub>, continues through NS<sub>1</sub> and ends in ES<sub>2</sub>. Application A<sub>1</sub> aims to transfer a RC message m<sub>1</sub> from task  $\tau_1$  to  $\tau_3$ , whereas A<sub>2</sub> seeks to transmit the time-triggered message m<sub>1</sub> from  $\tau_2$  to  $\tau_4$ . In the ESes, CPUs partition the two tasks so that the aforementioned spatial separation is achieved. In order to visualize the transmission flow better, the messages' paths are labeled on each step. Each of them has a distinct color green for RC and blue for TT.

Figure 2.13: "TT and RC message transmission example." Figure. [TSPS12], 4p.

#### 2.5.1 Time-Triggered Communication

The process starts with task  $\tau_2$  putting message  $m_2$  in frame  $f_2$  (a). Next, the frame is placed in buffer B  $_{1,T_r}$  designated especially for that frame (b). Each frame that arrives overrides the value stored in the buffer before because of the single cell that it has. A look up in the send schedule  $S_s$  (c) must be performed in order to follow the predefined offline scheduling done before the start of the transmission. Scheduling tables are stored in every end system and network switch in the cluster ( $S_s$  and  $S_r$ ). When the predefined moment comes, scheduler  $TT_s$  sends f to  $NS_1$  (d) through the data link between the two (e). The Filtering Unit (FU) is the first in the switch to receive the incoming frame. FU checks its the validity and integrity (f) and separates frames based on the type of communication they implement. The receiving schedule  $S_r$  gives information on whether the frame arrived in a certain window interval (g). If the it did and messaging is of type TT, the frame is forwarded to the receive scheduler  $TT_r$ (h). If the frame exceeds the predefined window interval or if it had already arrived, the data is dropped. This fault-tolerance mechanism is known as fault containment.

From then on communication resembles the pattern described above.  $TT_r$  places the frame in a specific buffer - in this case  $B_{1,T_x}$ . With correspondence to schedule  $S_s$  in NS<sub>1</sub>,  $TT_s$  sends the frame to its final destination - ES<sub>2</sub>. When it reaches the right partition -  $P_{2,1}$  - it is unwrapped and message  $m_2$  is read when the currently active task is  $t_4$ .

#### 2.5.2 Rate Constrained Communication

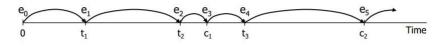

Like with Time-Triggered communication, the transmission starts by packaging message  $m_1$  in a frame (1). The first contrast comes with the queue, the frame is put in (2). It is one per virtual link and can contain multiple cells. The general difference, however, is that RC transmission is event-triggered. This implies that no scheduling tables are needed to oversee the time of sending and receiving in the end systems and network switches. Another consequence is that temporal separation is done through "bandwidth allocation". As mentioned before, TT transfer is predefined so TT messages don't have to worry about a particular mechanism for temporal separation once the offline scheduling is done. This is not the case with RC traffic seeing as it is dynamic. In order to apply "bandwidth allocation" for each channel, the protocol designer must define the minimum time interval between each consecutive pair of RC messages. That is the definition of the previously mentioned Bandwidth Allocation Gap (BAG). A key characteristic of BAG is that it must be less or equal to the reciprocal value of the rate at which a given frame is transmitted. BAG is defined by the Traffic Regulator (TR) (3). Let there be two TR tasks with different sized BAG that have two messages. Figure 2.14 depicts how these messages are multiplexed by the RC scheduler (4). So when both TRs try to send their message simultaneously, the phenomenon called jitter occurs. In this case the jitter is equal to the sum of the transmission duration of all the other messages that were sent before the particular message.

Figure 2.14: "Multiplexing two RC frames." Figure. [TSPS12], 5p.

Yet another key difference between TT and RC messages is presented when an RC one reaches TT (5) - the priority. Having a lower priority because of the lesser critical level, RC messages can be transmitted only when there are no TT messages around. Thus TTEthernet must provide a way to integrate the two so that the bandwidth is fully utilized and yet all traffic starting from the highest level of criticality - must reach its destination in time. The possible cases are two: a TT message is transmitted over the dataflow link and a RC message is sent by the scheduler for transmission, and the reverse. The former case is

trivial - TT messages have precedence of RC, so lower critical messages have to wait until the bandwidth is free. The latter case, however, is non-trivial - thus of greater interest. It will be discussed in an upcoming section in depth.

As previously described, once a frame is received by the Filtering Unit, it is then checked for validity and integrity. If the frame passes the test, it is sent to the Traffic Policy (TP) (7) which implements fault-containment just like TT (8). This is done by an algorithm called leaky bucket which looks at the time at which any given frame is received and that of the one before it. It then compares the result to the BAG defined for the virtual link. If the BAG has a lower value - the frame continues its transmission. If the BAG is greater then the frame is dropped. After that the procedure of reaching the designated task - in our case task 3 - resembles TT messaging.

#### 2.5.3 Integration Policies

There are three ways in which a network switch in TTEthernet deals with the conflict that arises when high priority message(TT) becomes ready for transmission while a low priority message(RC) is being relayed through the network: shuffling, timely block and preemption. All of them will be discussed in greater detail in this section with respect to their resource utilization, quality of transmission and other key aspects to the message transfer.

| Ongoing Low Priority<br>Transmission  |  |

|---------------------------------------|--|

| New High Priority<br>Transmission     |  |

| Output as produced<br>by preemption   |  |

| Output as produced<br>by timely block |  |

| Output as produced<br>by shuffling    |  |

Figure 2.15: "Integration Methods for High-Priority (H) and Low-Priority (L) Traffic." Figure. [TSPS12], 192p

In case of preemption, the transfer of the RC frame is discontinued. The minimal "silence" period is then executed on the active channel by the network switch, immediately followed by a TT message. *Real-Time Quality* is high because preemption makes sure that TT messages are transmitted with the lowest latency - constant and known in advance in the best case. *Resource utilization* is inefficient. In every case where a RC frame is withheld from completing its transfer, there needs to be a re-transmission. This, subsequently, results in a loss of bandwidth. The drawback can be fixed by using additional functionality for message reconstruction. In general the truncated messages must be perceived as faulty messages, so mechanisms for dealing with that are to be applied. One such mechanism can be the generation of a signal that breaks the rules for correctly generated RC messages. Thus the end systems that receive the traffic will be able to notice the difference.

The second option is timely block. It is available only if a TT frame is scheduled before the RC frame is fully sent through the dataflow link. If this happens, the RC frame is blocked on the link for a certain time period and TT communication is delayed. *Real-Time Quality* is high because delay of high critical traffic is constant, which implies deterministic behavior. *Resource utilization* is inefficient. Because of RC messages with unknown length, solutions implementing timely block must postpone communication for the maximum size of RC message that is defined. To address this low-criticality frames can contain their length as the value of field. Thus only RC traffic that can be fully transmitted is guaranteed to be relayed.

Lastly there is shuffling, which describes the exchange of priorities between TT and RC messages. In the case of shuffling a TT frame waits until the RC frame is being fully transmitted. The worst-case scenario is examined when the RC communication has the maximal length defined in the network. *Real-Time Quality* is low. Having to wait for multiple RC frames will degrade the performance substantially. As a relief comes the fact that TT messages are dispatched according to their static pre-scheduled time tables. Having that in mind synchronization based on the times known a priori reduces the jitter that is created because of the priority exchange *Resource utilization* is efficient because, unlike preemption and timely block, frames are not interrupted - thus no truncated traffic is present. So, in a sense, utilization is optimal for shuffling. A drawback of this approach is that it has increased complexity in scalability for TT communication. Also, although controlled and bounded, integration of BE traffic within shuffling may pose a problem especially when its source is unknown.

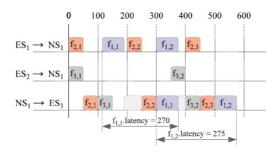

### 2.6 Example

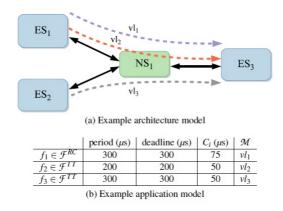

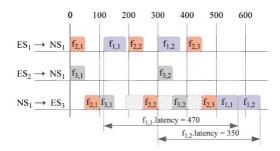

After describing the architecture model and communication in detail, the report supplies an example of how scheduling is performed in TTEthernet. The cluster presented here consists of three end systems  $(\text{ES}_1, \text{ES}_2, \text{ES}_3)$  and a single network switch NS<sub>1</sub>. There are also three virtual links that are used to transmit three frames. Figure 2.16(a) is used to provide visualization purposes. 2.16(b) gives the period, deadline, transmission time and virtual link for each frame. Timely block is used to manage ambiguities in the traffic.

Figure 2.16: "Example system model" Figure. [TSPS12], 5p.

The problem here is to find the best way to schedule both TT and RC messages so that they meet their deadlines. Because TT communication is pre-scheduled, a look up in the scheduling table S present in all ESes and in NS will be enough to determine if any deadlines are missed. The worst-case end-to-end delay needs be calculated when RC frames are to be scheduled. To portray the actual schedule order of communication, Gantt charts are given as Figure 2.17 for the initial scheduling and Figure 2.18 for the optimized variation. Both schedules present valid strategies for TT scheduling. The charts give the communication over the three dataflow links -  $[ES_1, NS_1]$ ,  $[ES_2, NS_1]$  and  $[NS_1, ES_1]$  - over 600  $\mu$ s time.

Frame  $f_1$  is event-triggered, which means that it can be scheduled in many ways considering the static scheduling of  $f_2$  and  $f_3$ . Figure 2.19 shows the situation where all the TT frames are dispatched as soon as possible i.e. their delay is minimal. Let frame  $f_1$  be sent from ES<sub>2</sub> to NS<sub>1</sub> at 105  $\mu$ s. A timely block is issued once the frame is compared to the higher priority frame  $f_3$ . Because the next instance of  $f_2$  interrupts its full transmission,  $f_1$  cannot finish the operation. Once all  $f_2$  and  $f_3$  frames are transferred,  $f_1$  is passed. This results in the worst-case end-to-end delay for  $f_1 - 470 \ \mu$ s, which makes it not schedulable, seeing as its deadline is 300  $\mu$ s.

Figure 2.17 shows a greatly reduced worst-case delay - 270  $\mu$ s - making it schedulable. This is the result of 50  $\mu$ s delay of frame f<sub>3</sub> 's second instance, which gives frame f<sub>1</sub> the needed time to get scheduled.

With these visual representations of the scheduling process, the reader is able to identify the enormous effect of RC over TT traffic.

Figure 2.17: "Initial TT schedule" Figure. [TSPS12], 6p.

Figure 2.18: "Optimized TT schedule" Figure. [TSPS12], 6p.

# 2.7 Fault-tolerance

TTEthernet is designed with the intention of being fault-tolerant. This is achieved through various capabilities that the protocol comprises. Firstly it is characterized by its ability to implement redundancy. This can be done in multiple elements of the network - end systems, network switches and other segments. The degree to which redundancy is incorporated within the system is dependent to the amount of fault-tolerance that is required in the system.

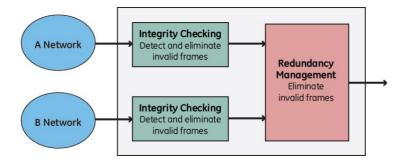

Figure 2.19: "A and B Networks." Figure. [Pla05], 13p.

**Redundancy management** is a property of the whole network in general because TTEthernet comprises of two, independent of each other, networks A and B(see Figure 2.19). This means that there is double amount of generated traffic that is routed through the network. Also for each created frame, the receiving end system will obtain two identical frames.

| Ethernet Header | IP Header | UDP<br>Header | UDP Payload<br>Avionics Subsystem<br>Message                                       | Seq. No. | FCS |

|-----------------|-----------|---------------|------------------------------------------------------------------------------------|----------|-----|

| byte 14         | 20        | 8<br>€        | و المسلحة 17 1472 مسلحة 10 | 1        | 4   |

|                 | ¢         |               | and Payload                                                                        |          | ,   |

Figure 2.20: "AFDX Frame and Sequence Number." Figure. [Pla05], 13p.

A problem that arises is how to distinguish that a replica packet has been received. To address this problem TTEthernet frames are equipped with a field of length 1 byte called sequence number. This byte is situated between the IP header and payload and the FCS fields. Because the frame is of fixed size the byte used as a sequence number is taken from the IP/UDP payload (see Figure 2.20).

The functionality that checks a frame's sequence number is named "Integrity Checking". It is applied by the end system upon receiving of the frame for each link and network port. If the communication has already been presented to the end system the packet is dropped, otherwise it passes through.

A visual summary of the process of redundancy management is provided within Figure 2.21.

After that comes **scalability**. It increases latent failure detection probability on a multi-platform system and decreases implementation costs for systems that expand rapidly. Different configurations with equality between the end systems(multi-master synchronization) or multiple end systems being controlled from a single one(master-slave synchronization) are possible. In systems that have similar criticality levels TTEthernet provides "service history".

Next the protocol integrates **tolerance to multiple inconsistent faults**. This means that when multiple concurrent failures occur in a network with equally

Figure 2.21: "Receive Processing of Ethernet Frames." Figure. [Pla05], 13p.

ranked end systems, they will be dealt with in a cost-efficient way. Faults can be present either in the communication or in the end system(inconsistent-omission faulty communication path or end system) or simultaneously in both.

Figure 2.22: "TTEthernet provides implicit fault tolerance mechanisms." Figure. [Pla09b], 7p.

Network switches and end systems are implemented so that they can operate with **guardian functions** (see Figure 2.22). These functions aim to determine whether the traffic throughout the network is working according to the initial intentions of the designers. In case an element has become faulty, the guardian simply disconnects it from the rest of the network segments. To give a higher level of fault-tolerance, a system may implement multiple guardians at various places. In a system where a single network switch interconnects multiple end systems, the guardian function may be implemented as a central bus guardian. This allows for masking a set of end systems that have become faulty. (e.g. experiencing the "babbling idiot" state where they sent repetitive messages in a short time interval). If the architecture is distributed, the guardian function takes care that no faulty nodes corrupt the communication bus. Thus TTEthernet provides tolerance to arbitrary end systems failures.

Lastly the protocol is designed with **self-stabilization capabilities**. This means that after a case of multiple faults across a distributed system, synchronization will be re-established.

## 2.8 Summary

TTEthernet is a protocol made to accommodate the needs of hard real-time systems. Moreover its design allows for integration on distributed systems where transmission types vary in safety integrity levels. Each type is supplied with specific fault-tolerant mechanisms in order to insure that safety-critical constraints are met. TTEthernet can extend an existing network to different topologies located on heterogeneous media without introducing major changes to its current state. This is achieved through the protocol's main network components - end systems and network switches. TTEthernet's scalability and fault-tolerance facilitate its suitability for a wide range of applications where problems like cost, efficiency, safety and predictability are of key importance.

# Chapter 3

# Modeling and Simulation

This chapter presents the notion of modeling and simulation in the context of system development. It discusses key characteristics of a simulation such as selecting input probability distributions, random number generators and how to perform output data analysis. The two simulation paradigms - continuousand discrete-event - are presented and compared by their appropriateness with respect to the master thesis project. A closer look at the existing world views of discrete-event simulation provides theoretical background needed to support the simulator implementation.

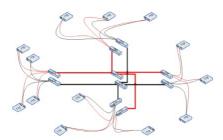

# 3.1 System

The main concept that lays in the center of this chapter is that of a **system**. It is a set of interacting or interdependent components (e.g. people, machines) forming an integrated whole. As an example Figure 3.1 depicts a Local Area Network (LAN) which is essentially a system consisting of computers that communicate with servers. To describe it we need to observe the parameters that define the system at a given point in time. This is the definition of **state**. In the displayed computer network these state variables could be the number of servers that are currently working, the computers that are being serviced, etc.

Figure 3.1: "Computer Networking - LAN Networking". Digital image. Accessed 16 August 2013

When talking about types of systems we can distinguish between two types discrete and continuous. A discrete system is one for which the state variables change instantaneously at separated points in time. The LAN above is a discrete system - a change to its state of occurs for example in case of a server malfunction or when a computer receives an acknowledgment from a server. A server can either be functional or nonfunctional - it doesn't have an intermediate state. The term continuous system is used to represent state variables changing continuously with respect to time. A system like that is a ship traveling in the sea. The ship's state changes with the continuous change of its speed and position through time.

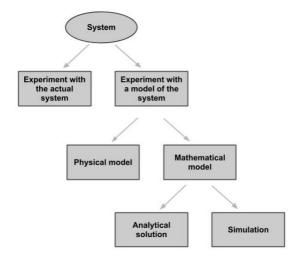

#### 3.2 Model

There are many ways one can study the workings of a system. This is visualized in Figure 3.2. The two main ways are - performing actual experiments with the system and construction of a model used to represent the system. The choice of a model over actual experiments can easily be explained with the following example. If the LAN network from Figure 3.1 has one million computers, an actual experiment would be a poor choice seeing as the funds needed for its fruition are formidable. This is the case with a great number of systems in real life and that is way building a model is often a favorable choice.

Figure 3.2: "Ways to study a system". Figure. [LK99], 4p.

A model is a simplified representation of a system which is created with the purpose of studying it. It consists of a set of assumptions, concerning the aspects of a given system, that affect the problem under investigation. A model is expressed through mathematical or logic relationships of entities that give understanding about the behavior of the system in detail.

There are various types of models each of which will briefly be discussed here. They are:

- static vs dynamic

- deterministic vs stochastic

- discrete vs continuous

**Static** simulation models depict a "snapshot" of a system - a single moment in its evolution. It can also display a system without any notion of time. A **dynamic** model, on the other hand, is a representation of system that evolves with the progress of time.

Determinism is predictability. Thus if a model does not comprise probabilistic (random) elements it is a **deterministic**. For a given set of input values such models repeatedly produce the same output. In the case where a model contains element introducing randomness to the system, it is a **stochastic** model.

The definitions for **discrete** and **continuous** models resemble the ones given previously for the existing types of systems.

Taking into account the definitions given above, the model of TTEthernet protocol used for the simulation can be categorized as discrete, dynamic, stochastic.

Figure 3.3: "Construction of a model". Figure. [BCNN00]

#### 3.2.1 Verification and Validation

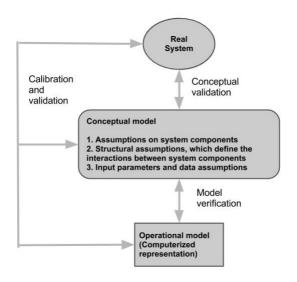

As discussed the first process of building a model is deciding what kind of model best replicates the existing system. When a conceptual model is constructed the question whether it is a valid representation of the real system arises. The answer to this question has three parts - verification, validation and credibility. Because credibility address the project lifecycle with respect to a company or another institution (i.e. have the model approved by a manager) this section focuses on the former two parts.

The creation of a model is a repetitive process that is described in Figure 3.3. It can be done through a comparison either between the model and operational model or between the model and the real system. In the former case the process is called **verification**. It checks whether the conceptual model is accurately portrayed by the operational model (computerized representation). As this is

a computer program, this process will often result in debugging the simulation. The complexity of this task grows with that of the modeled system. This is the case because the amount logical paths in big systems tend to become extremely large.

Verification of a model can be done through the following methods:

- creation of flow diagrams

- study of the reasonableness of output from the operational model

- verification that input parameters have not been changed

- documentation of working process

- visualization of working process (GUI, animation)

- debugging the program (trace)

After a comparison between the conceptual and operational model has been made a step called **calibration** is introduced. It is simply the process of refining (readjusting) the model by removing flows discovered during the verification and fine-tuning it. This process continues until both models have an acceptable degree of difference in the output that they produce. The calibration can be done through either a subjective or objective test.

The comparison between a conceptual model and the real system and their corresponding behavior is called **validation**. It should be noted that absolute validity of a model cannot be achieved. This is because a simulation model is an approximation of the real system. Thus a model can be made more valid the more it is calibrated. It is also true that a model is developed with specific requirements. It can be the case that two models of a same system have different purposes and so differ in their operation.

Validation of simulation models in a three-step approach. The first step is the creation of a high face validity model. This is a subjective measure of the extent to which this selection appears reasonable. It is tested by having an external view - from people knowledgeable with the real system - test the model output for admissibility and discover flaws in the process. The following step is validation model assumptions. It can be done though:

• structural assumptions - describe how the system operates and usually involve simplifications and abstractions of reality

• data assumptions - based on the collection of reliable data and correct statistical analysis of the data

The last step is done by comparing the model to real system input-output transformations. In order to perform this step, however, there should be data recorded while observing the system. They will be used to support to calculate the necessary system characteristics. The validation test consists of comparing the output from the real system to that of the model for the same set of input conditions.

## 3.3 Simulation

As seen previously in Figure 3.2 the generation of a mathematical model leads to two options of studying a system - perform analytic solution or create a simulation. The goal of the master thesis is to model and simulate the TTEthernet protocol, therefore this section defines the term simulation. It also gives theoretical support and explanation to key design decisions when constructing a computer simulation.

**Simulation** is an imitation of the operation of a real-world process or system over time. It simulates potential changes in the system by evaluating the mathematical model numerically. The data accumulated by the simulation allows the study of systems in design stage - before their actual construction. It also gives insight of the desired characteristics of the model. A simulation enables the generation of artificial history of the system and helps draw conclusions for the real system.

#### 3.3.1 Selecting input probability distributions

A stochastic simulation uses random inputs. These could be arrival times, arrival order, etc. For such simulations there needs to be a source of randomness - a defined input probability distribution. There are three approaches that can be used in order to specify a distribution - trace-driven, define empirical distribution, fitted "standard" distribution.

The term **trace-driven** simulation denotes usage of the generated random inputs themselves directly in the simulation as data values directly in the simulation. The pros with this choice are that the simulation is done with historically ordered stream. This is very useful when trying to compare a simulator to an existing system. In favor of this approach is also model validation as it allows for easy comparison between pre-generated output with that of the simulator. The problems with trace-driven simulation are that it just reproduces historical results which results in insufficient data for a multiple simulation runs.

The second way to handle random variables is to use them to define an **empirical distribution** function. Its strengths lay in generating values between the min and max data points. This is valued in the cases where it is known in advance that a random variable can never exceed a certain value. We also use empirical distribution when theoretical distributions may not be an adequate "fit" for observed data. The shortcomings of this approach lay in the fact that values will never be larger than max (the upper bound). This means that extreme events cannot be simulated. Output data and cumulative probabilities are generated for given input data - cumbersome if input is large.

**Fitted "standard" distribution** describes inserting a theoretical distribution form to the random variables through standard techniques of statistical inference. This approach helps generate values outside the observed data range and provides a compact way of data representation. An obstacle to using this approach can be the lack of an adequate "fit" for observed data.

The trace-driven approach was the one chosen in the master thesis project. As previously stated, this approach allows for comparison with existing outputs. This is the case here since in chapter 5, there is a comparison between the results of an analysis and the simulators.

#### 3.3.2 Random Number Generation

A stochastic simulation with a probability distribution needs to use random numbers (random variates). A "good" arithmetic random number generator (RNG) has the following characteristics:

- provides a independent and identical uniform distribution of random values in the interval of [0,1]. This is also known as IID U (0,1).

- no correlation between values

- good time and space complexity

- ability to reproduce given stream (subsegment of numbers produced by the generator) of values

- ability to reproduce separate streams (independent generators) of values. The last two bullets can be used to study the correct workings of a simulator

The TTE thernet simulators use a Prime Modulus Multiplicative Linear Congruential Generator (PMMLGC) proposed by Marse and Roberts (1983). It is utilized when the arrival times for RC and BE messages are generated.

#### 3.3.3 Output Data Analysis

Figure 3.4: "Types of simulations with regard to Output Analysis". Figure.

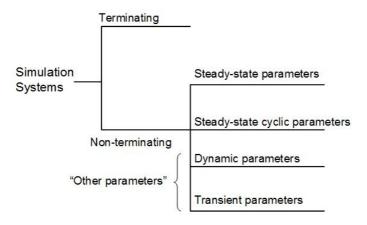

Studying the output of a simulator plays a role as important as that of making it - especially when using empirical or "fitted" standard distributions. In order to analyze the data accumulated by the simulator, it needs to be classified with respect to its terminating conditions. Figure 3.4 shows the various possibilities. The two basic types here are terminating and non-terminating. **Terminating** simulations are those for which there is a "natural" event E that specifies the length of each run. Because of the limited operation that such simulators have, designing them aims to study the operation control. It should be noted that in terminating simulators only conditions that are specific to the system should be set as initial since they affect the measures of performance. **Non-terminating** simulators are the ones for which there is no event specifying the run. They have no concrete duration of execution, thus their focus is on long-term problems.

For non-terminating steady-state systems the following parameters are of interest:

- steady-state parameters

- steady-state cycle parameters certain parameters change with given cycles during simulation

- dynamic parameters certain parameters change over time, but not cyclic

- transient parameters there are certain significant "events" that interrupt the operation of an otherwise steady-state system

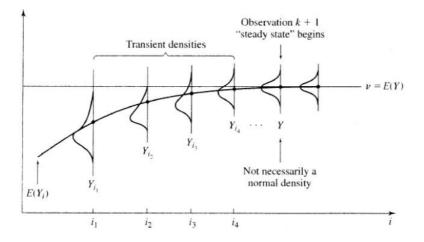

The output of the simulator can be also viewed as a stochastic process. Therefore the analysis of the data can behave as a part of either a transient or a steadystate distribution. A **transient**state is an interval of time in which our system is either "warming up" or taking its time to respond to progress. **Steady-state** is the opposite of transient. Steady-state is a condition where our system continues with an easily predictable behavior and few values of it are changing (if any are changing at all). Figure 3.5 gives a comparison between both distributions.

Figure 3.5: "Transient and steady-state density functions". Figure. [LK99]

# 3.4 Simulation paradigms

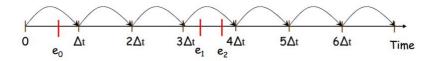

Previously the report presented separated systems in two types - continuous and discrete. This differentiation can also be done with respect to the simulation paradigms. Explanation to both types is provided in the form of two examples. Firstly, a simulation of a given system which evolves through time is of interest. A system like that is the weather forecast. The humidity in a city changes daily - continuously with respect to time. The easiest way to view this would be to make a diagram of the humidity values - most likely a continuous curve. Thus events that are simulated are continuous hence the name **continuous-event**

simulation (CES).

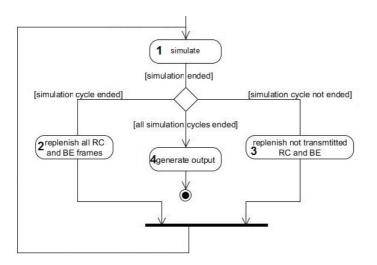

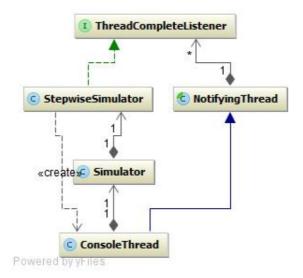

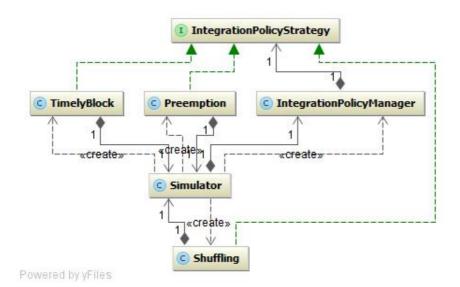

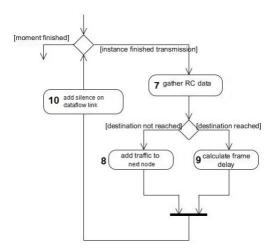

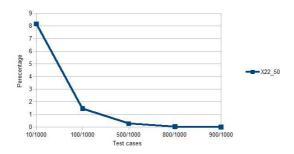

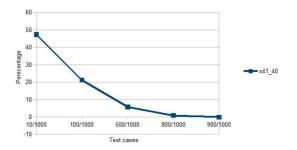

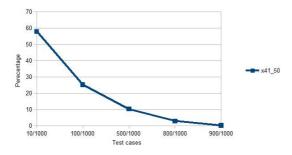

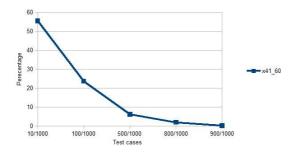

As a counter example is to examine the queue in a cinema. Customers arrive at the counter, they get serviced and leave. Variables of interest could be the time spent waiting in line, service time, number of waiting customers, etc. Plotting this would result in multiple continuous lines with breaks in between them. This definition describes a step function. The events - the change in the number of customers - are discrete variables. The name of this type of simulation is **discrete-event** (DES).